Other Parts Discussed in Thread: CONTROLSUITE

Hello,

We purchased the DesignDRIVE Development Kit IDDK v2.2.1 and I have a question on the IDDK_PM_Servo_F2837x project.

It is stated in the file of IDDK_PM_Servo_F2837x.c as follows:

-------------------------------------------------------------------------------------------------------------

//Enable DAC output

DacaRegs.DACOUTEN.bit.DACOUTEN = 1;

DacaRegs.DACCTL.bit.SYNCSEL = 5; // sync sel 5 meanse sync from pwm 6

-----------------------------------------------------------------------------------------------------------------

I suppose that the ePWM6SYNCO signal will update the DACVALA register according to C codes listed above.

It is also stated in the file of IDDK_PM_Servo_F2837x.c as follows:

------------------------------------------------------------------------------------------------------------------

SyncSocRegs.SYNCSELECT.bit.EPWM4SYNCIN = 0; //EPwm1SyncOut

EPwm4Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN;

EPwm5Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN;

EPwm6Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN;

EPwm6Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm6Regs.TBPHS.bit.TBPHS = 2;

EPwm6Regs.TBCTL.bit.PHSDIR = TB_UP;

---------------------------------------------------------------------------------------------------------------------

Then I suppose that the ePWM6SYNCO signal corresponds to the EPwm1SyncOut.

I assume that the EPwm1SyncOut means the ePWM1SYNCO signal.

It is stated in the function PWM_1ch_UpDwnCnt_CNF( ) of the file IDDK_PM_Servo_F2837x.c as follows:

------------------------------------------------------------------------------------------------------------------

(*ePWM[n]).TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; // sync "down-stream"

--------------------------------------------------------------------------------------------------------------------

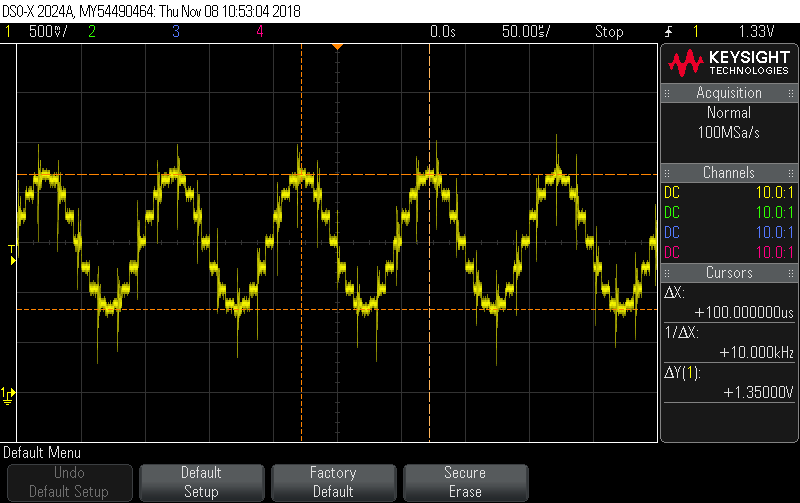

The time base counter (TBCTR) of the ePWM1 module may be cleared to zero at the period of INV_PWM_TICKS, which is 10,000 or 100us.

Therefore I suppose that the DACVALA register is to be updated every 100us.

Please review my reasoning on the update rate of the DACVALA register and point out where I have misunderstood it if I am wrong.

Thank you for your guidance.

G. Kim