Other Parts Discussed in Thread: MOTORWARE

Hi,

I have a couple of queries regarding the ADCs.

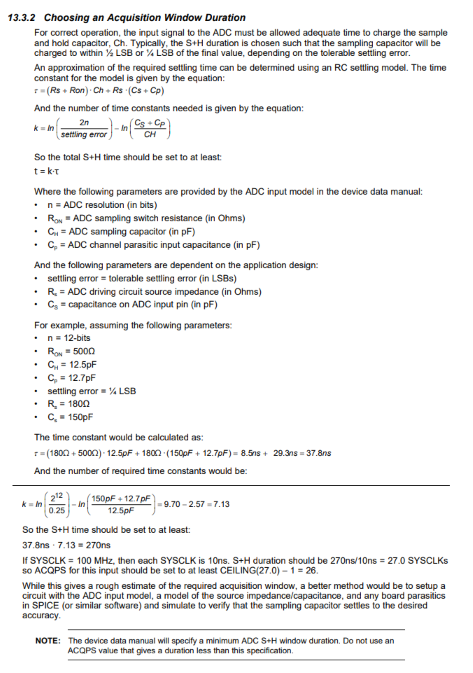

1. The voltage feedback is simply a resistor divider with a filter capacitor (sized for a particular cut-off frequency). What will be its effect on the input impedance of ADC? Will I have to change the acquisition time? Can you let me know what calculations should I perform so that the ADC S/H capacitor reaches within 0.5LSB margin?

2a. The HAL tutorial in the motorware project shows how to add an ADC for a potentiometer. It suggests triggering the ADC on ADCINT1. It mentions the end of conversion of channel 7 generates ADCINT1. Can you let me know which line of code does that? Also, which document describes the complete ADC sequence of operation for this application?

2b. I have a sin-cos encoder and I have to configure 2 ADC channels to it. I will be using it to calculate the angle and speed instead of the sensorless algorithm. Can you let me know when should I trigger these 2 ADCs and how important it is to trigger it with current ADCs?

Thanks