Other Parts Discussed in Thread: LMR62421, EK-TM4C1294XL, BOOSTXL-DRV8320RS, , LAUNCHXL-F280049C

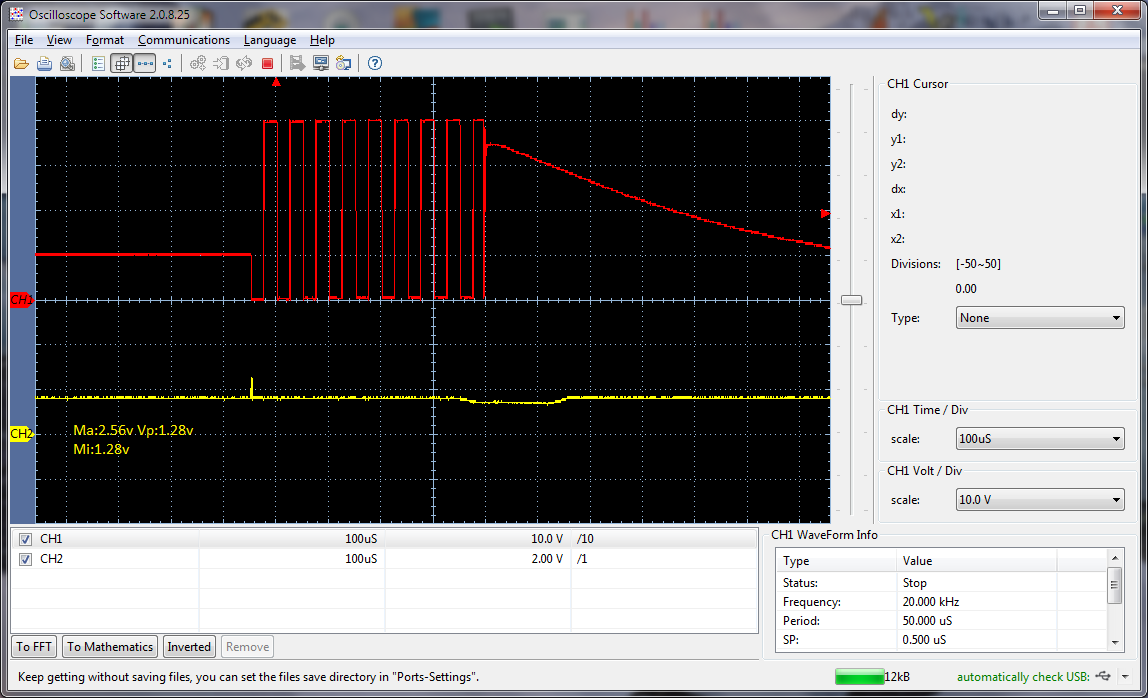

It would seem there is an isolation issue when not powering XDS110 via VBUS and L101 is removed to use external +5vdc supply. That L1 removal being necessary as there is no 3v3 buck on the launchpad side of isolation barrier. The host DC inverter provides 750mA +5vdc via buck down +40vdc. As a result JP1, JP2, JP3 must be strapped so U101 can buck +5v down to +3v3 for the target MCU and XDS110. No +5 VBUS power comes from USB host computer.

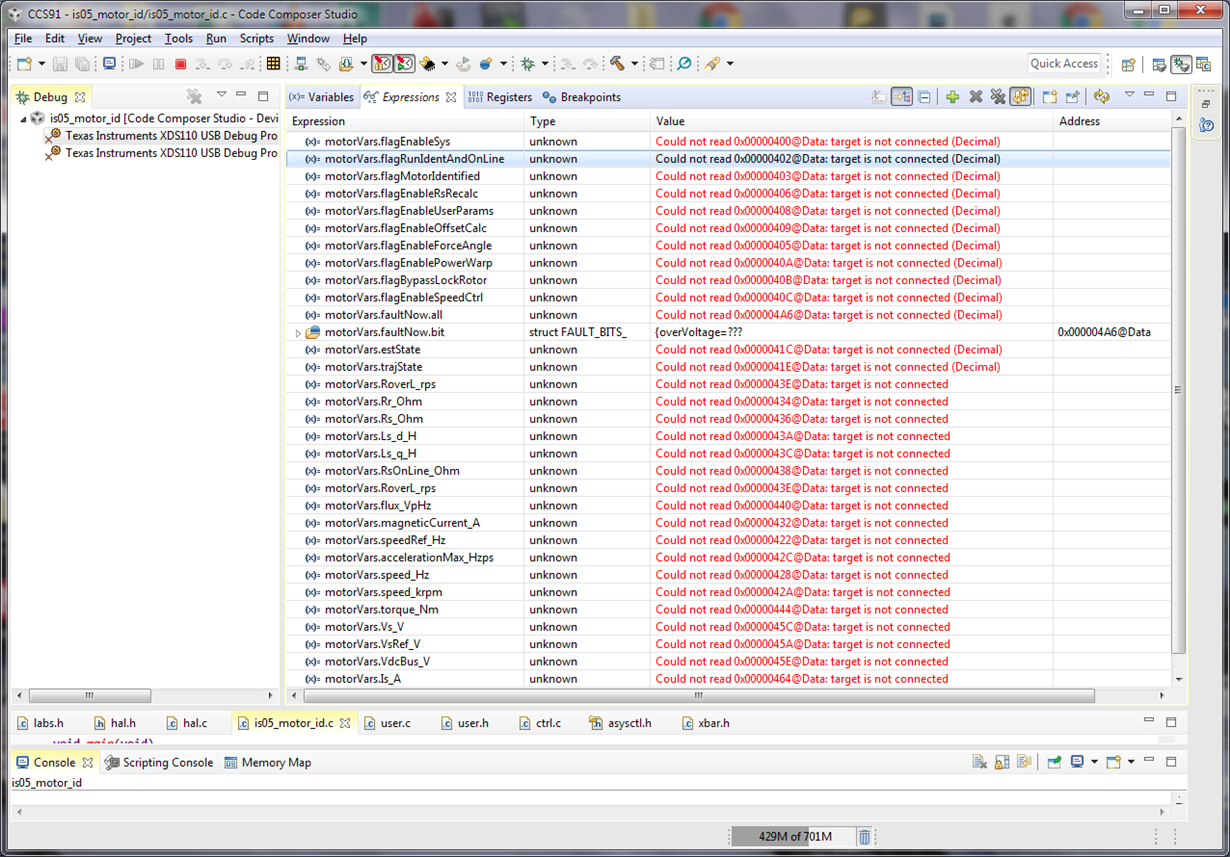

The result of no isolation being an immediate XDS110 disconnect from host USB CCS real time debug when ADC Offset calibration is simply enabled.

Oddly a +3v3 boost +5v (U5) exists target side of isolation but no buck down from +5v to 3v3 to power target MCU when isolated from U101 via Jp1, Jp2, Jp3.

1. Can U5 be made to buck +5v down to +3v3, rather than boost?

2. What is easy solution to regain XDS110 isolation and or use U5 to buck +5 to +3v3? It powers target MCU now with Jp1,Jp2, jp3 in place but has NO XDS110 isolation from target side.

3. Should we just remove JP1 for adding ground isolation (U3) when external +5v powers header J3 pin 21, ground J3 pin 22?

The Isolation Boundary (U3) schematic makes no sense VBUS1=USB_VBUS (JP3) and VBUS2 is tied to +3v3 on the other side of isolation. Seemingly +3v3 via JP2 should be tied to VDD2 of U5 and not VBUS2. Seemingly VB2 is actually +5v, removing JP3 for +5v isolation and JP2 for VDD2 +3v3 isolation? Has the isolation boundary (U5) been incorrectly depicted? If it has been incorrectly depicted can TI please provide a corrected drawing so we can understand how the barrier should work when Jp1, Jp2, Jp3 are removed or left in place?