Dear SIr,

we are developing controller based on 28376S and have some issue to reach specifc SPI configuration.Our controller is the SPI Master and sends 3xSPI Word each of 12bit with SPI Clock of 1Mhz,

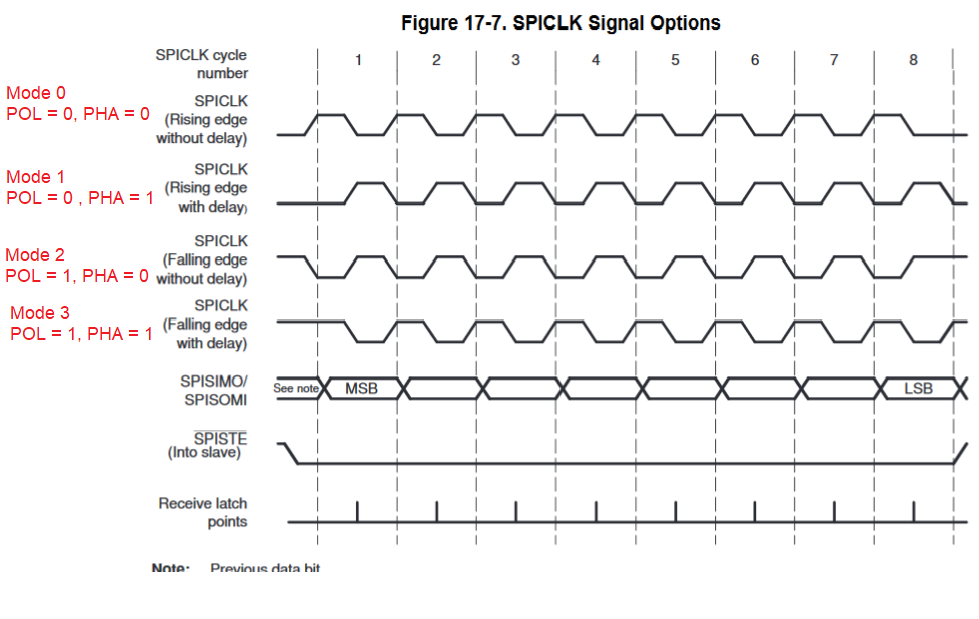

the Slave clock scheme is clocking data on the falling edge (this is how we configure as well ) and latching on the rising (SPi Master as well.).

the issue that we are seeing is when setting SPI with Clock polarity =1 (e.g. shift on falling and latch on rising ) the SPI CLK is at high during start of fram (e.g CS is going to low) , which cause us to miss 1 bit

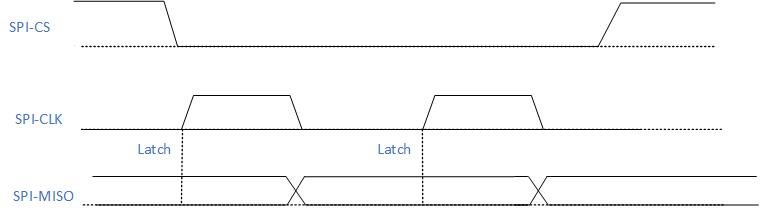

what we need is the SPI Clock to start at low level during start of frame , but latch on the rising edge as shown below , how can it be accomplished ?