Dear team:

One of my customers had some problems when using can communication module of f28335 and PC through can analyzer. The details are as follows:

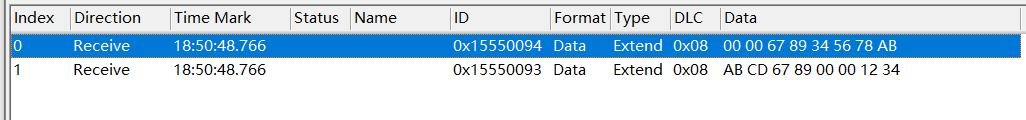

He configured the receiving mailbox of f28335 as the sender of remote frame, and set the corresponding RTR and TRS. However, the remote frame was successfully sent out only once in the test. As shown in Figure 1 (only this time is successful, and after that, no remote frame sent by DSP has been received).

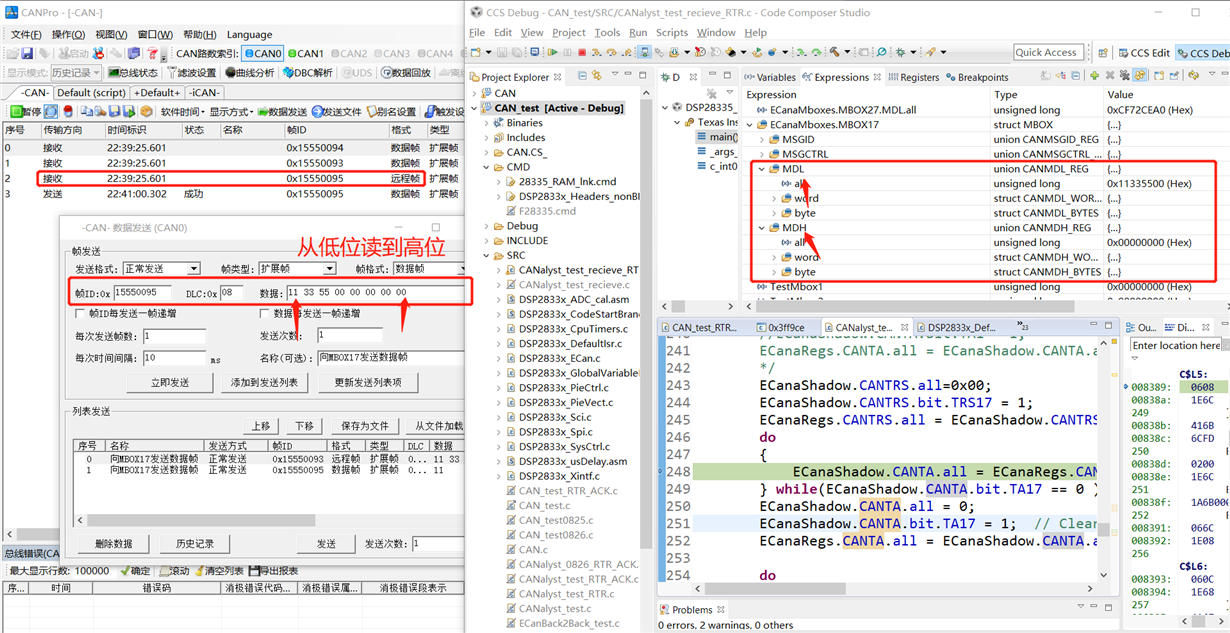

The same code, then do the same experiment, remote frames can not be sent out. At the same time, no matter how the TRS and RTR are set, the bits read from the register are not set successfully according to the instruction, and are always kept at 0. The code is as follows:

Set ID:

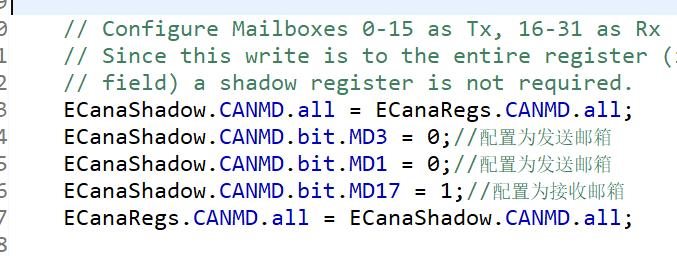

Configure mailbox direction:

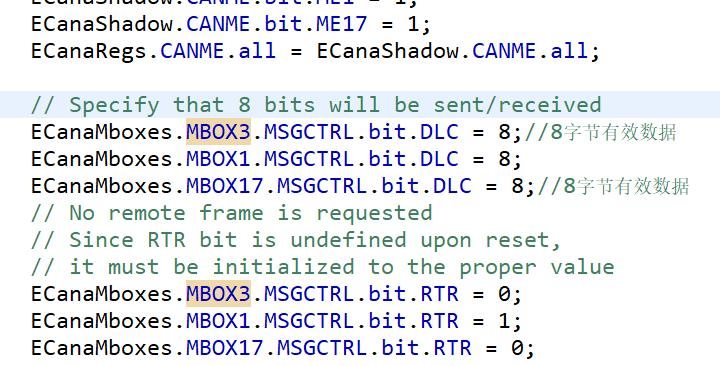

Enable mailbox, set DLC, RTR (from the register observation, it is found that these configurations failed)

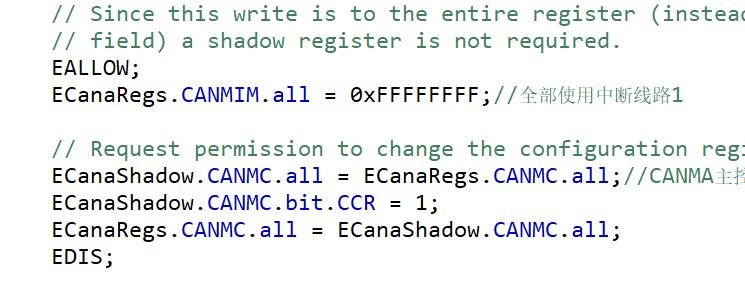

Other related configurations:

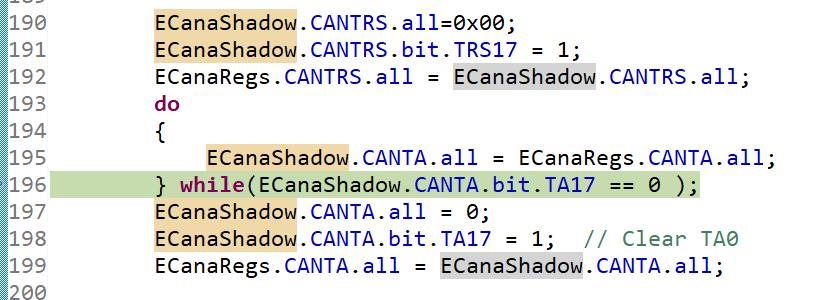

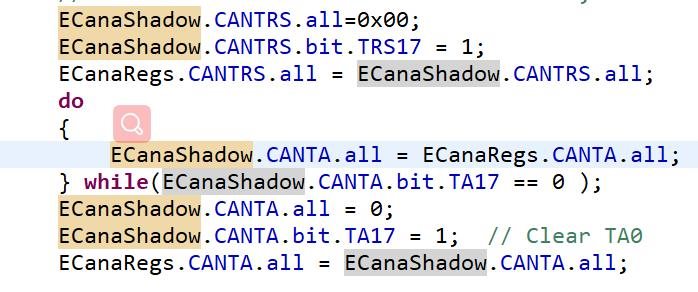

Set TRS (it will be stuck in the while loop, ta17 is always 0, trs17 and rtr17 are both 0, and remote frames sent are not monitored on the bus)

Msgid of receiving mailbox MBOX17 is set to B5550095 (AAM = 1, AME = 0)

Is there any problem with the above program configuration?

Best Regards