Other Parts Discussed in Thread: C2000WARE

Tool/software: Code Composer Studio

Hello,

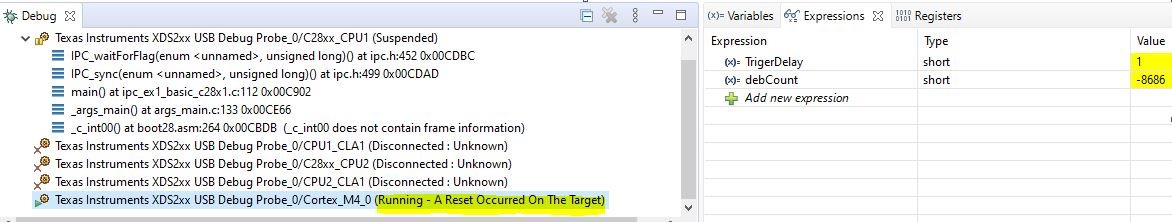

I have enabled the watch dog timer and hope that a CM reset triggerd when the WD counter is overflowed.

I stop calling SysCtl_serviceWatchdog() in INT_TIMER0, and the timer interrupt stop, I think the WD counter has been overflowed, but there is no reset happened.

1. In the TRM "41.5 Watchdog Timer", it said it will enable CMNMIWD and trigger a reset. However I enable CMNMICFG by SysCtl_enableGlobalNMI() and set CMNMIWDPRD=100. Nothing happended. How could I do?

2. After above, I trigger a IPC_INT0 by software to CM, a CM reset happened. What is the case described in the TRM?

Thanks