Other Parts Discussed in Thread: MSP430FG4619

Hi all,

This is the setup

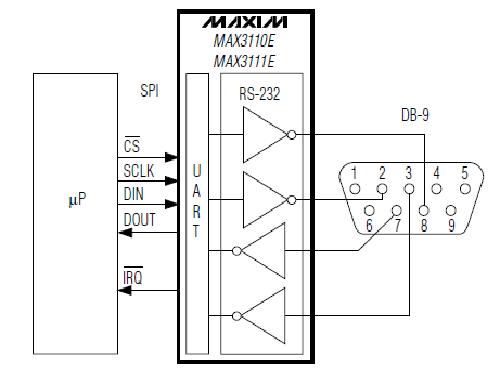

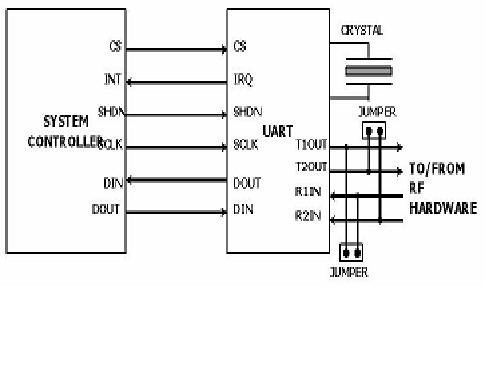

The MSP430(System controller) is the master and communicates on SPI with UART on MAX3111E .

MSP430 is the master and I am using 3 wire mode with CS to control SPI commn.

The flow of the communication is like this

CS low

Write to MAX3111E configuration register (16 bit) - to set the baud rate etc

CS high

CS low

Read the configuration register to see if the configuration is done properly

CS hi

But I am not able to configure the MAX3111E properly. The configuration is not happening properly (I am writing #CC 0Ch but reading #40 40h).

I think communication is not getting setup properly.

I wanted to confirm two things

1) Do I have to setup the baud rate of UART as per the SPI SCLK(using SMCLK-32768*32 Hz.

2) Also, after sending the command for read configuration register do I have to send dummy bytes to receive data.

3) Do I have to monitor UCBUSY to see if any activity is happening on SPI before deasserting CS. Currently I am using UCA0TXIFG and UCA0RXIFG .

I am attaching the code and also 1882.MAX3110E-MAX3111E(RF LINK).pdfthe datasheet of MAX3111E.

Thanks........