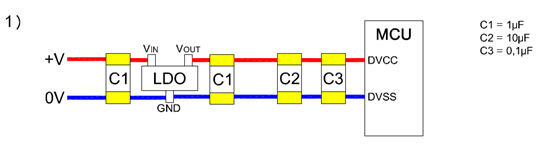

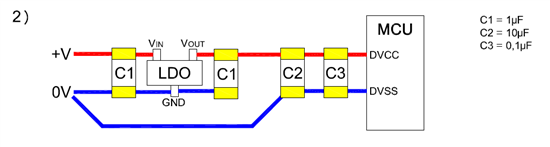

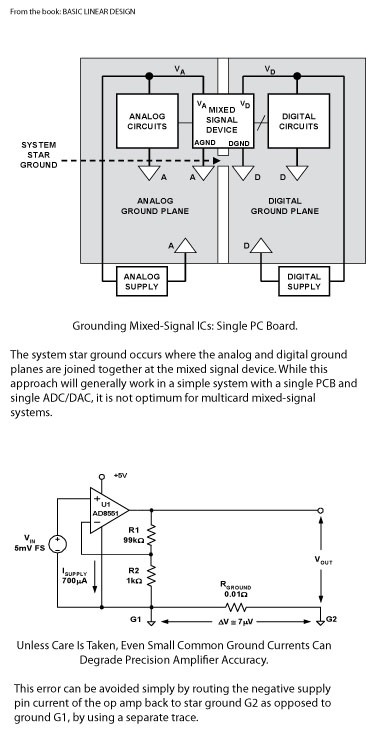

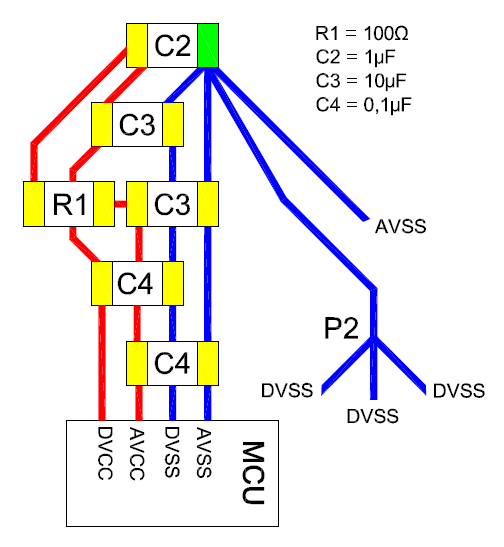

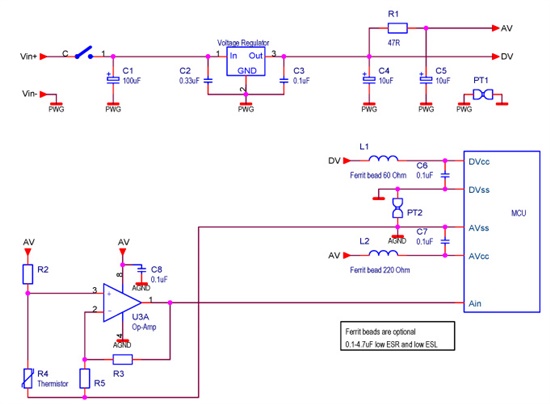

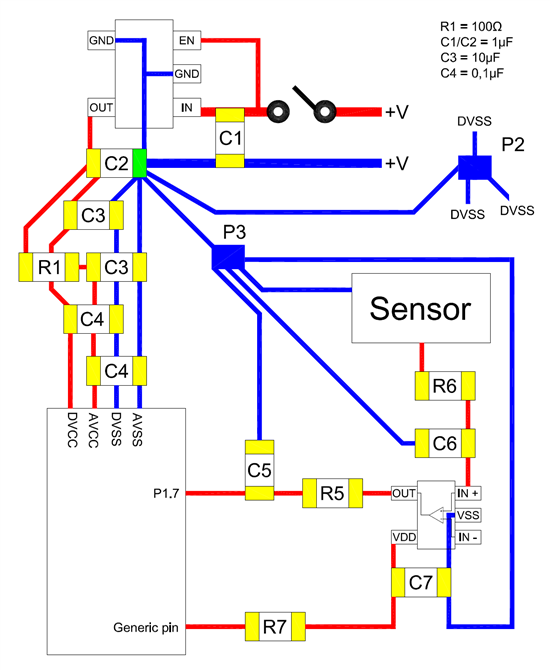

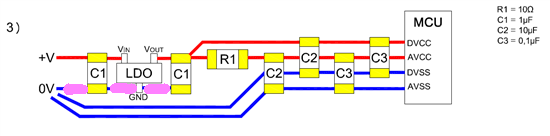

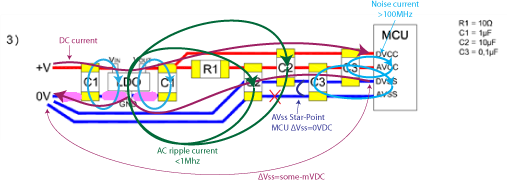

1) The microcontroller is the MSP430G2553 (in TSSOP package), decoupled with the “0,1μF + 10μF combo” capacitors.

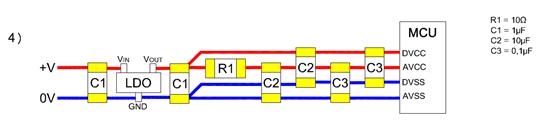

2) The supply voltage comes from an LDO (2.5V), properly decoupled.

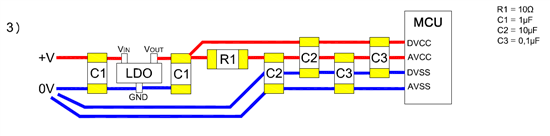

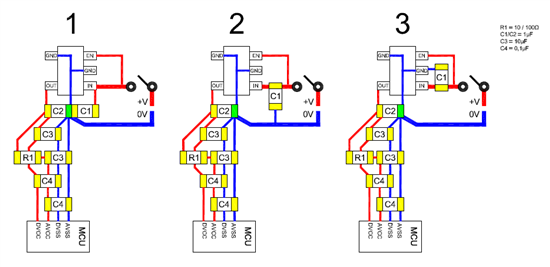

3) The source of the analog input is the output of an OpAmp; as written in its datasheet, “The output pins are low-impedance voltage sources”.

4) I’ve placed a low-pass filter BEFORE the OpAmp, and I’ve properly decoupled the OpAmp. The VCC pin of the OpAmp is directly connected to a generic pin of the microcontroller, which turns ON the OpAmp when needed.