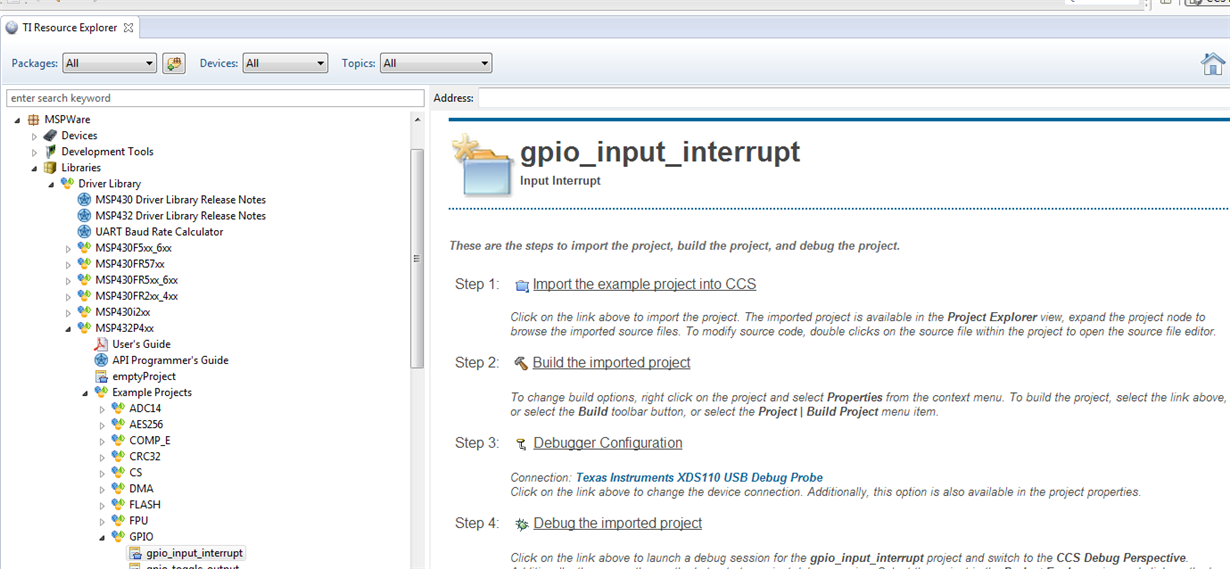

I am modifying example "msp432p401_p1_03", where an external interrupt is generated for port1.1 with the button. I'm using CCS 6.1.2.00015

I have extended this example to do the same for port2.7, with another button (for argument's sake).

But it is not working; only interrupt 1 is generated, as was provided in the example.

If I change the order in ISER[ ] the program doesn't work at all.

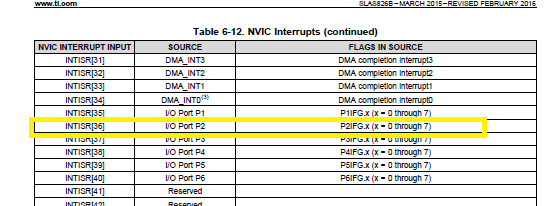

NVIC->ISER[2] = 1 << ((PORT2_IRQn) & 31);

NVIC->ISER[1] = 1 << ((PORT1_IRQn) & 31);

I also tried

NVIC_EnableIRQ(PORT1_IRQn); // Enable PORT1 Interrupt

NVIC_EnableIRQ(PORT2_IRQn); // Enable PORT2 Interrupt

but that doesn't work either: as long as interrupt 2 has not been generated, interrupt 1 works. Once interrupt 2 has been generated, interrupt 1 stops functioning.

Questions:

1) what to do?

2) does anybody know where to get information about practical use of the NVIC?

Here is the code:

#include "msp.h"

int main(void)

{

/* Hold the watchdog */

WDTCTL = WDTPW | WDTHOLD;

P1DIR = ~(uint8_t) BIT1; // p1.1 input

P2DIR = ~(uint8_t) BIT7; // p2.7 input

P1REN = BIT1; // Enable pull-up resistor P1.1

P2REN = BIT7; // Enable pull-up resistor P2.7

P1IFG = 0; // Clear all P1 interrupt flags

P2IFG = 0; // Clear all P2 interrupt flags

P1IE = BIT1; // Enable interrupt for P1.1

P2IE = BIT7; // Enable interrupt for P2.7

P1IES = BIT1; // Interrupt on high-to-low transition

P2IES = BIT7; // Interrupt on high-to-low transition

// NVIC_EnableIRQ(PORT1_IRQn); // Enable PORT1 Interrupt

// NVIC_EnableIRQ(PORT2_IRQn); // Enable PORT2 Interrupt

NVIC->ISER[2] = 1 << ((PORT2_IRQn) & 31);

NVIC->ISER[1] = 1 << ((PORT1_IRQn) & 31); // Enable Port 1 interrupt on the NVIC

/* Configure Port J */

PJDIR |= (BIT2 | BIT3); PJOUT &= ~(BIT2 | BIT3);

/* PJ.0 & PJ.1 configured for XT1 */

PJSEL0 |= BIT0 | BIT1;

PJSEL1 &= ~(BIT0 | BIT1);

/* Starting LFXT in non-bypass mode without a timeout. */

CS->KEY = CS_KEY_VAL ;

CS->CTL1 &= ~(CS_CTL1_SELA_MASK | CS_CTL1_SELB);

CS->CTL1 |= CS_CTL1_SELA__LFXTCLK; // Source LFXTCLK to ACLK & BCLK

CS->CTL2 &= ~(CS_CTL2_LFXTDRIVE_MASK); // Configure to lowest drive-strength

CS->CTL2 |= CS_CTL2_LFXT_EN;

while (CS->IFG & CS_IFG_LFXTIFG)

CS->CLRIFG |= CS_IFG_LFXTIFG;

CS->KEY = 0;

/* Turn off PSS high-side supervisors */

PSS->KEY = PSS_KEY_KEY_VAL;

PSS->CTL0 |= PSS_CTL0_SVSMHOFF;

PSS->KEY = 0;

/* Enable PCM rude mode, which allows to device to enter LPM3 without waiting for peripherals */

PCM->CTL1 = PCM_CTL0_KEY_VAL | PCM_CTL1_FORCE_LPM_ENTRY;

/* Enable all SRAM bank retentions prior to going to LPM3 */

SYSCTL->SRAM_BANKRET |= SYSCTL_SRAM_BANKRET_BNK7_RET;

__enable_interrupt();

SCB->SCR |= SCB_SCR_SLEEPONEXIT_Msk; // Do not wake up on exit from ISR

/* Setting the sleep deep bit */

SCB->SCR |= (SCB_SCR_SLEEPDEEP_Msk);

/* Go to LPM3 */

__sleep();

}

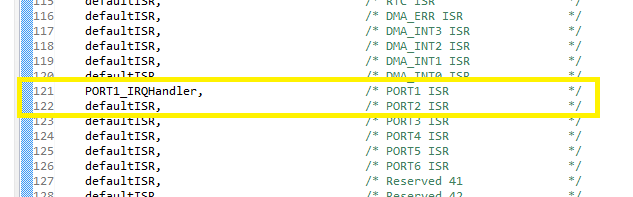

void PORT1_IRQHandler(void)

{

if(P1IFG & BIT1){

P1OUT^=BIT0;

}

P1IFG &= ~BIT1;

}

void PORT2_IRQHandler(void)

{

if(P2IFG & BIT7){

P1OUT^=BIT0;

}

P2IFG &= ~BIT7;

}