Hi

When MSP430F5x wakes up from LPM0/1, tWAKU-UP-FAST and tWAKE-UP-SLOW are applicable as same as wake-up from LPM2/3/4 ?

I guess YES, but Data Sheet and User’s Guide only mention wake-up time from LPM2/3/4.

Why?

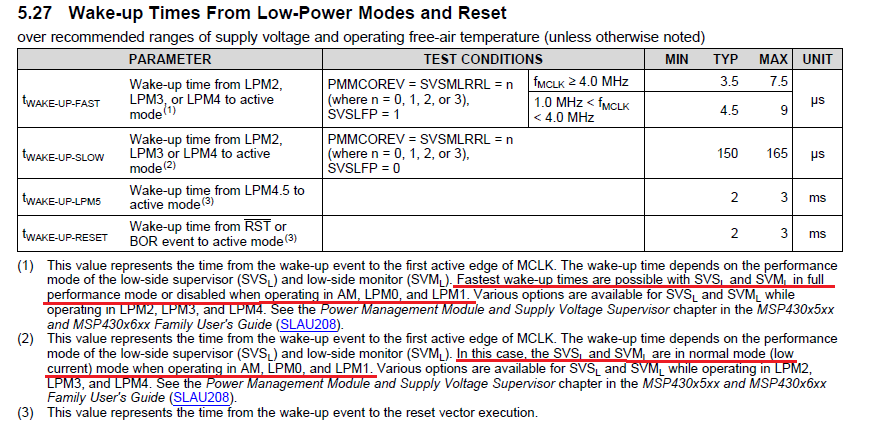

Example: Table from User's guide (slau208o)

Table from data sheet

Thanks and regards,

KoT