Hello,

I'm currently trying to configure the MSP430FR5969 to read from a Si1133. Communication is to be done through I2C.

My difficulty is with the proper order of configuration for this interface. From what I've read (through other discussions and datasheets), I should be able to make use of eusci_b_i2c and drivelib packages.

The user in this thread is more or less trying to accomplish the same thing.

This is how I see the process working from the Master side:

- Initialize GPIO pins (SDA, SCL)

- Initialize Master parameters

- Initialize Master

- Set the Slave Address

- Set the mode (Transmit in this case)

- Enable I2C block

- Transmit Data

- Stop

The the 'Transmit Data' Part is what I am questioning.

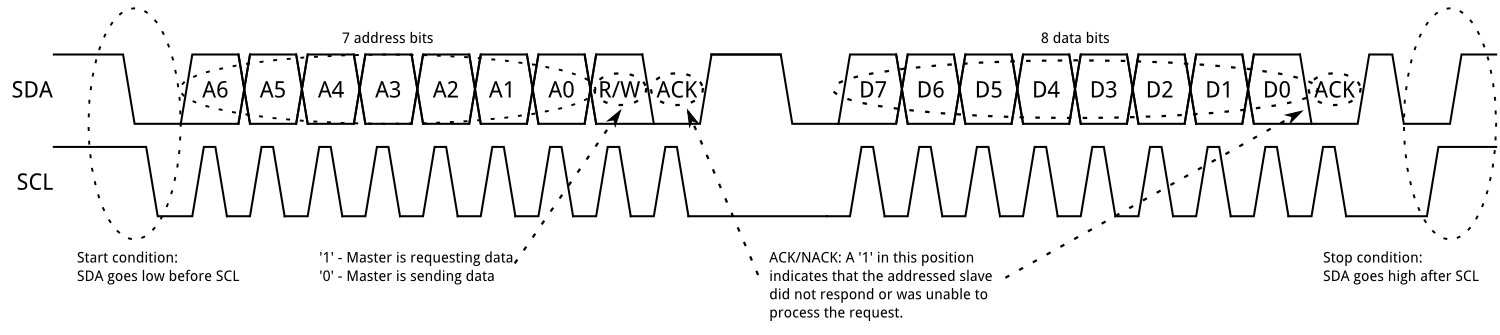

According to the Si1133 Datasheet, a simple write sequence consists of the following order of commands (from the Master):

- Start

- Send Slave Address

- Set Write

- Receive ACK

- Send Register Adress

- Receive ACK

- Send Data

- Receive ACK

- Send Stop

Now the eusci_b_i2c library provides functions that send a START, then DATA, then STOP, all in one call. But I don't believe that's what I want to do here.

As a starting point, all I would like to do is send the SLAVE Address, then read the ACK. Where exactly is the ACK sent? I imagine it's flag, just unsure of what one.

Perhaps using getInterruptStatus is a way to check?

Also, is it possible to check if the ACK was received while in Debug?

Feel free to ask for any clarification. For context, I'm a student trying to learn bare-metal C.

Thank you