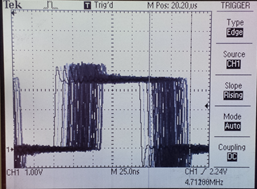

I am working on a product that requires low-jitter timing pulse with a 1ms period. I'm generating a pulse using MSP430FR5969 timer in compare mode, with no interrupt involved, with the timer set up to pulse the capture/compare reg. associated OUT bit. I am puzzled as to why I am seeing significant jitter in the periodic pulse. The jitter that I measure leading edge to trailing edge is approx. 15ns, and jitter measured leading edge to leading edge of next pulse is over 250ns along with some low-frequency drift.

I am wondering why the jitter is so large? The only relavant spec I found in the data sheet is the DCO jitter of 2ns. I am using the DCO at 16MHz as source for MCLK and SMCLK, and the timer source is SMCLK.

Here's my timer init code:

void tmrA0Init (void) {

// configure P1.1 for use as TA0.2

P1DIR |= BIT1;

P1SEL1 &= ~BIT1;

P1SEL0 |= BIT1;

TA0CCR0 = 1024; // CCR0 drives high (reset/set mode)

TA0CCR2 = 2048; // drives TA0.2 low

// Cap/comp 2

TA0CCTL2 = CM_0 | CCIS_0 | CLLD_0 | OUTMOD_7 ; // Reset/Set output mode, no interrupt

TA0CTL = CNTL_0 | TASSEL__SMCLK | ID_0 | MC__CONTINUOUS;

}

Any insights into this jitter would be appreciated.

Thanks,

John