Is the default frequency of the SMCLK 1.048MHz as seen here http://e2e.ti.com/support/microcontrollers/msp430/f/166/t/157922?What-is-MSP430F5XXX-SMCLK-default-frequency-at-Power-on-

or is it automatically calibrated to 1.000 MHz by default?

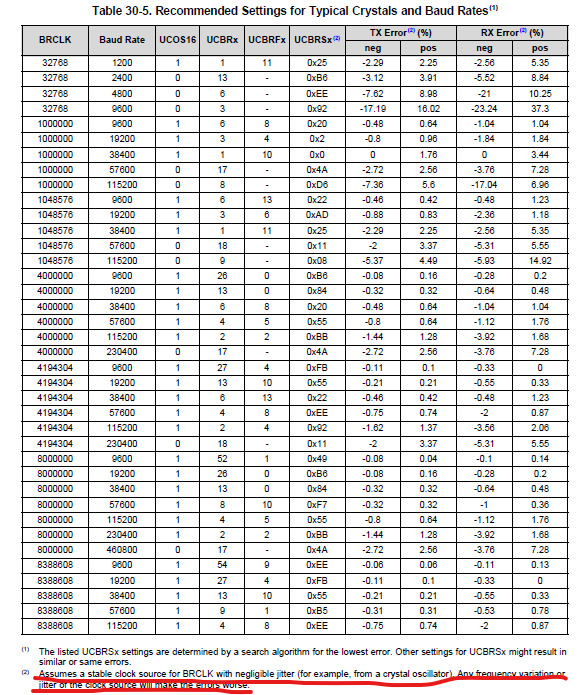

My goal is to choose the correct UCBRx UCBRFx and UCBRSx for UART transmission. I am not sure if the BRCLK would be 1048576 or 100000 by default.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.