Tool/software: Code Composer Studio

Dear team,

Customers have tested SD24_B and found problems when using it.

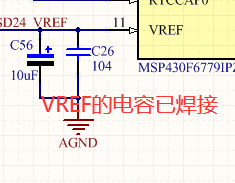

When the input voltage is 0, the result register still has a value, the 100nf capacitor has been connected, the code is modified on the official routine, the code is as follows.

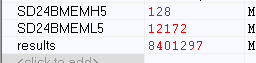

The customer uses channel 5. In order to eliminate interference, both the positive and negative terminals are connected to DGND, but there are still very large values, and the value in the SD24BMEML5 register has been changing。

#include <msp430.h>

/* Unsigned integer to store SD24_B conversion result */

unsigned long results;

void main(void)

{

WDTCTL = WDTPW | WDTHOLD; // Stop WDT

SD24BCTL0 = SD24REFS | SD24SSEL_1; // Select internal REF

// Select SMCLK as SD24_B clock source

SD24BCCTL5 |= SD24SNGL; // Single conversion

SD24BINCTL5 |= SD24INTDLY0; // Interrupt on 3rd sample

SD24BIE |= SD24IE5; // Enable channel 2 interrupt

__delay_cycles(0x3600); // Delay for 1.5V REF startup

while (1)

{

SD24BCCTL5 |= SD24SC; // Set bit to start conversion

__bis_SR_register(LPM0_bits | GIE); // Enter LPM0 w/ interrupts

__no_operation();

__no_operation(); // SET BREAKPOINT HERE

}

}

#if defined(__TI_COMPILER_VERSION__) || defined(__IAR_SYSTEMS_ICC__)

#pragma vector=SD24B_VECTOR

__interrupt void SD24BISR(void)

#elif defined(__GNUC__)

void __attribute__ ((interrupt(SD24B_VECTOR))) SD24BISR (void)

#else

#error Compiler not supported!

#endif

{

switch (SD24BIV)

{

case SD24BIV_SD24OVIFG: // SD24MEM Overflow

break;

case SD24BIV_SD24TRGIFG: // SD24 Trigger IFG

break;

case SD24BIV_SD24IFG0: // SD24MEM0 IFG

break;

case SD24BIV_SD24IFG1: // SD24MEM1 IFG

break;

case SD24BIV_SD24IFG5: // SD24MEM2 IFG

results = SD24BMEMH5; // Save CH2 results (clears IFG)

results = (results << 16) | SD24BMEML5; // Concatenate lower and upper words

break;

default:break;

}

__bic_SR_register_on_exit(LPM0_bits); // Exit LPM0

}

The link on E2EChina is

Please help.