Other Parts Discussed in Thread: EK-TM4C123GXL, TM4C1294NCPDT, SEGGER

Tool/software: Code Composer Studio

Hello again,

Now I'm with another EK-TM4C1294XL :D and hopefully this one will last longer.

Anyway, I'm facing a problem, this problem specifically:

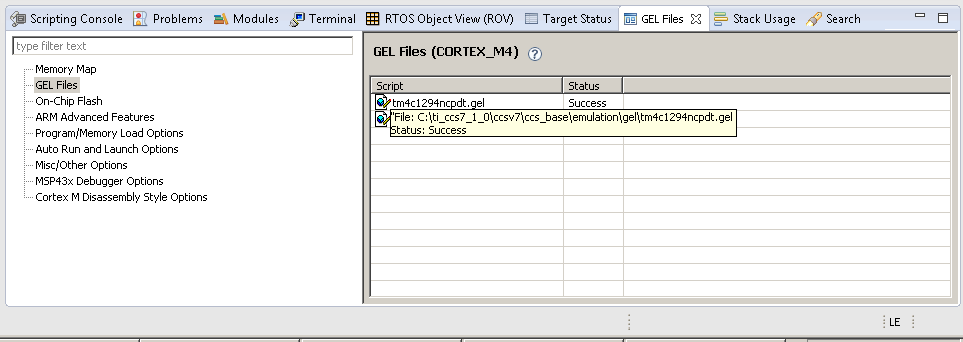

CORTEX_M4_0: GEL Output:

Memory Map Initialization Complete

CORTEX_M4_0: Trouble Reading Memory Block at 0x400fe000 on Page 0 of Length 0x4: Debug Port error occurred.

CORTEX_M4_0: Error initializing flash programming: Target failed to read 0x400FE000

CORTEX_M4_0: Loader: One or more sections of your program falls into a memory region that is not writable. These regions will not actually be written to the target. Check your linker configuration and/or memory map.

CORTEX_M4_0: Trouble Writing Register PC: Target is not halted or failed to halt after step.

CORTEX_M4_0: Can't Run Target CPU: Target is not halted or failed to halt after step.

CORTEX_M4_0: Trouble Halting Target CPU

This occurs when I use those functions:

inline void InitWatchdog(void)

{

ROM_SysCtlPeripheralDisable(SYSCTL_PERIPH_WDOG0);

ROM_SysCtlPeripheralDisable(SYSCTL_PERIPH_WDOG1);

ROM_SysCtlPeripheralReset(SYSCTL_PERIPH_WDOG0);

ROM_SysCtlPeripheralReset(SYSCTL_PERIPH_WDOG1);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_WDOG0);

ROM_SysCtlPeripheralEnable(SYSCTL_PERIPH_WDOG1);

while(!ROM_SysCtlPeripheralReady(SYSCTL_PERIPH_WDOG0) || !ROM_SysCtlPeripheralReady(SYSCTL_PERIPH_WDOG1));

ROM_WatchdogReloadSet(WATCHDOG0_BASE, g_SysClock*0.1);

ROM_WatchdogReloadSet(WATCHDOG1_BASE, FREQ_PIOSC*0.5);

ROM_WatchdogResetEnable(WATCHDOG0_BASE);

ROM_WatchdogResetEnable(WATCHDOG1_BASE);

ROM_SysCtlResetBehaviorSet(SYSCTL_ONRST_WDOG0_SYS);

ROM_SysCtlResetBehaviorSet(SYSCTL_ONRST_WDOG1_SYS);

ROM_IntDisable(INT_WATCHDOG);

ROM_IntPendClear(INT_WATCHDOG);

ROM_WatchdogIntClear(WATCHDOG0_BASE);

ROM_WatchdogIntClear(WATCHDOG1_BASE);

ROM_IntPrioritySet(INT_WATCHDOG, 0x00);

ROM_WatchdogIntEnable(WATCHDOG0_BASE);

ROM_WatchdogIntEnable(WATCHDOG1_BASE);

ROM_IntEnable(INT_WATCHDOG);

ROM_WatchdogEnable(WATCHDOG0_BASE);

ROM_WatchdogEnable(WATCHDOG1_BASE);

while(!ROM_WatchdogRunning(WATCHDOG0_BASE) || !ROM_WatchdogRunning(WATCHDOG1_BASE));

ROM_WatchdogLock(WATCHDOG0_BASE);

ROM_WatchdogLock(WATCHDOG1_BASE);

while(!ROM_WatchdogLockState(WATCHDOG0_BASE) || !ROM_WatchdogLockState(WATCHDOG1_BASE));

}

void WatchdogIntHandler(void)

{

ROM_WatchdogIntClear(WATCHDOG0_BASE);

ROM_WatchdogIntClear(WATCHDOG1_BASE);

}

On my other Tiva (EK-TM4C123GXL) this code works just fine. Why is that happening?