Other Parts Discussed in Thread: DRV8305, , , LAUNCHXL-F280049C

1.VCPH charge pump

Customer would like to know timing diagram of "PVDD、VCPH、CP1L、CP1H、CP2L、CP2H" in tripler mode and double mode.

They would like to know how to generate PVDD+10V.

2.VVCPH_OVLO

What kind of situation is supposed, VCPH become over 14V.

3.VVCPH_UVLO2 ,VVCP_LSD_UVLO2

What kind of situation is supposed, VCPH,VCP UVLO work.

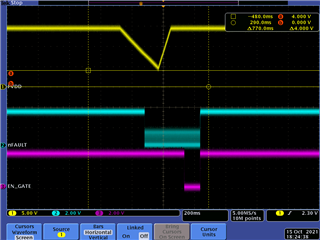

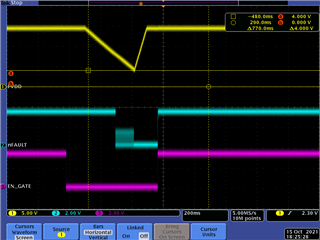

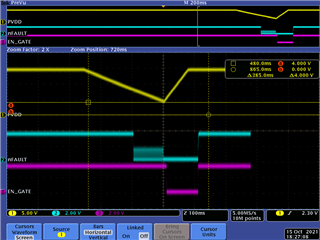

4.EN_GATE and nFAULT

When EN_GATE is always low, please let us know nFAULT pin behavior in this situation.

5.Variation of IDRIVE

Please let us know variation of IDRIVEP_HS,IDRIVEN_HS,IDRIVEP_LS,IDRIVEN_LS.

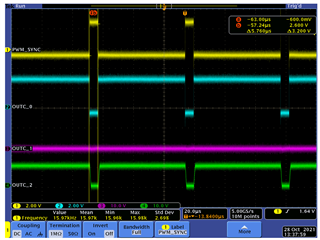

6.VDS_OCP

Please let us know variation of tBLANK,tVDS.

7.VDRAIN pin

Please let us know how much sink current of VDRAIN pin.