Hello,

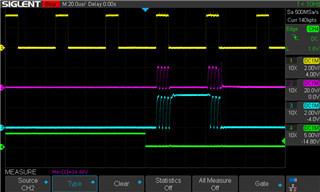

I was testing latched OCP mode and I found this weird issue. After an OCP occurs, nFAULT goes low and FETs are HI-z as expected. However in this state, if nSLEEP is driven low, the FETs look like they open momentarily:

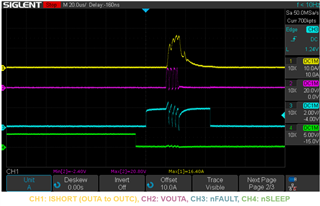

Note that to perform this test, a short is applied between OUTA and OUTC, hence current spiking up when the FETs open. It is weird that nFAULT is pulsing like so. The next test shows the same procedure except this time without the short:

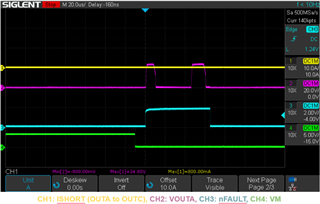

Here it looks like there are two instances where FETs open? This time, the nFAULT line looks clean though.

Any idea to what might be happening?

Jerome