Other Parts Discussed in Thread: CSD88539ND

Hi Team,

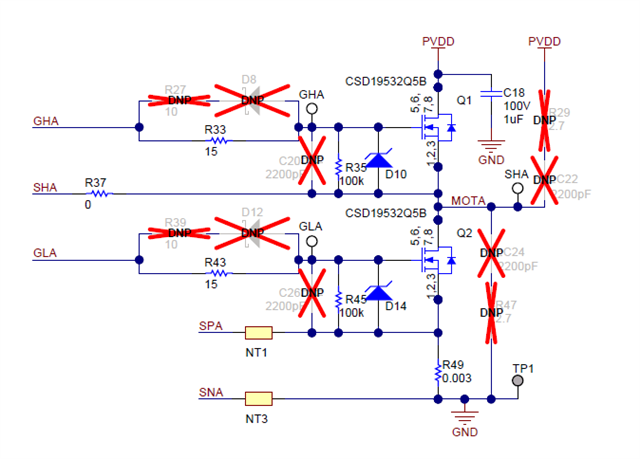

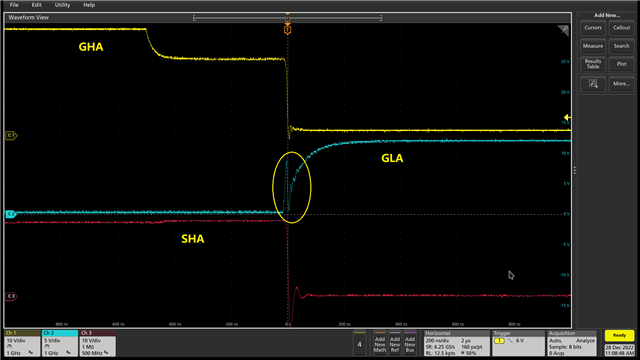

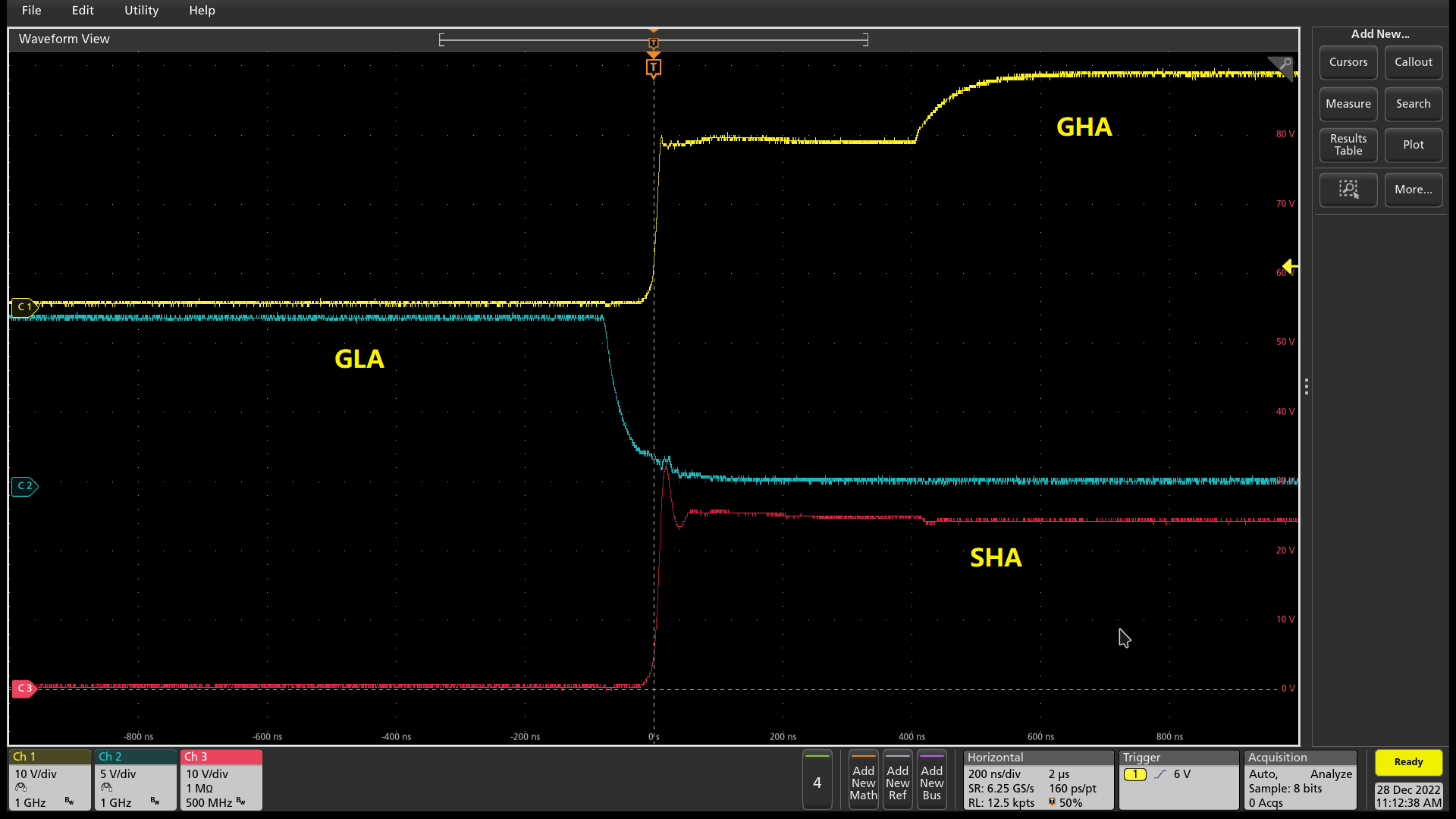

As shown in the figure below, csd88539nd is used for the MOS tube;

Schematic reference: DEMO_MD030A(001)_Sch;

The motor is a 13W BLDC motor, is this because of its insufficient drive capability? What improvement could I make?

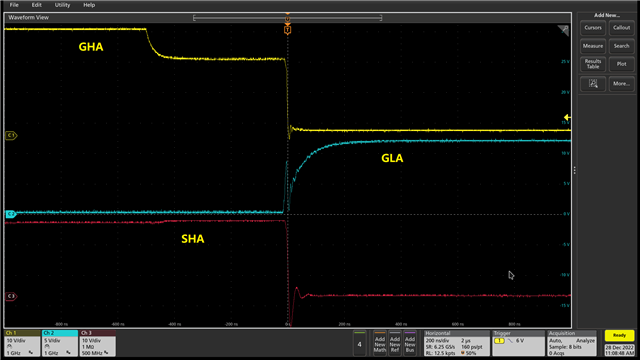

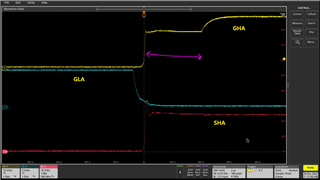

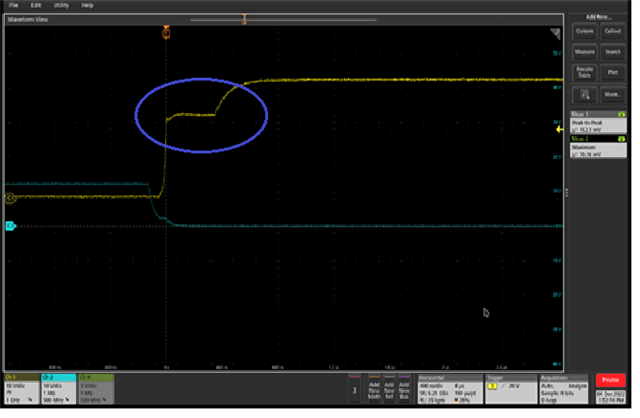

This is the VGS waveform generated when the upper tube MOS is turned on. It has a long plateau period.

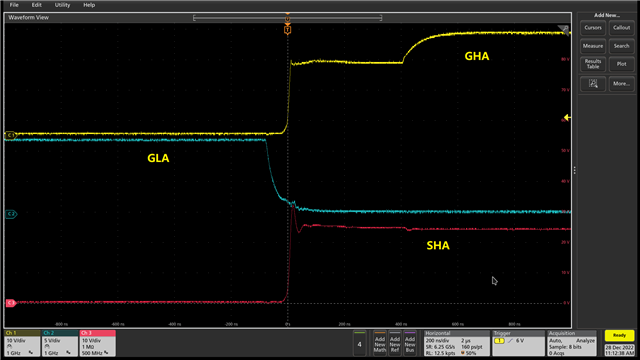

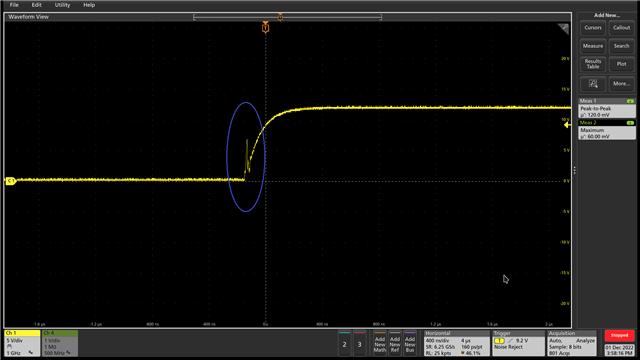

This is the VGS waveform generated when the lower tube MOS is turned on. It can only be opened with a large return channel.

Kind regards,

Katherine