Other Parts Discussed in Thread: DRV8876

Hi team,

could you help to answer the following questions on DS? thanks

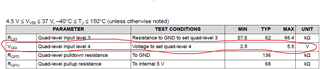

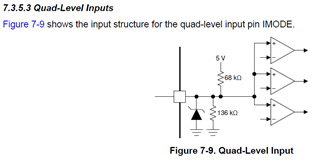

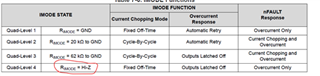

- 1. IMODE configuration has 4 ways, Level 4 is the most suitable for customer application (ordinary DC motor running for long time), but there is a problem, the corresponding pulldown resistance is Hi-Z, That means dangling. As an input pin, the dangling is susceptible to interference, resulting in erratic operating conditions. Are there ways to improve?

- Whether the PWM control mode can use 100% duty cycle

- What do PH and EN mean in PH/EN control mode? What is the abbreviation of the word?

thanks