Other Parts Discussed in Thread: CSD88599Q5DC

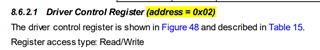

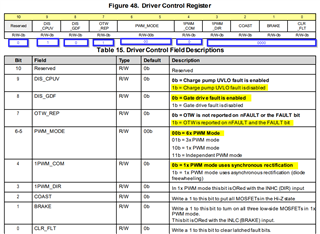

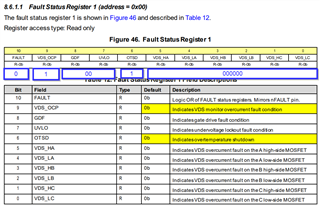

We've had a couple motor drivers stop functioning with the state as reported in the thread title. It gives no other debugging information (no other bits are set in either of the fault registers). From probing it appears that logic and other supplies are ok. I imagine that we've done something to damage the IC, I'm wondering if anyone is aware of the scenario that might help us further debug the cause that would lead to this state.