Other Parts Discussed in Thread: DRV8705-Q1, DRV8702-Q1

Hi team,

My customer uses DRV8703-Q1 in their project and now they met an issue, could you please help give some comments? Thanks!

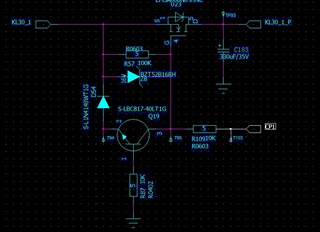

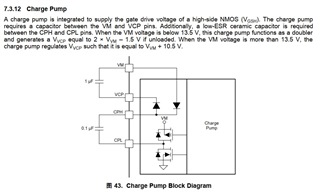

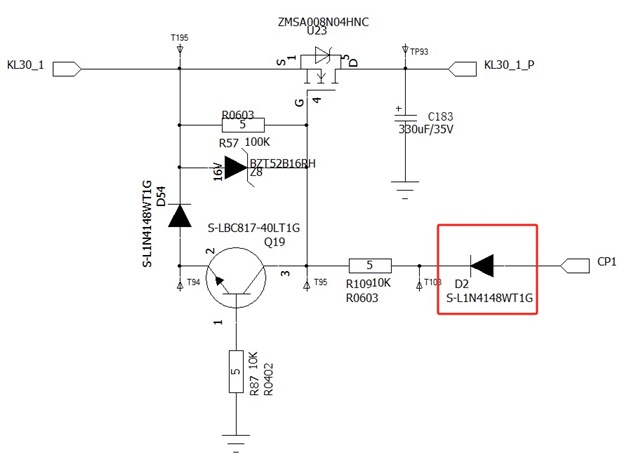

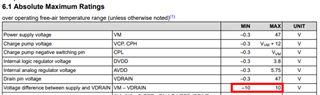

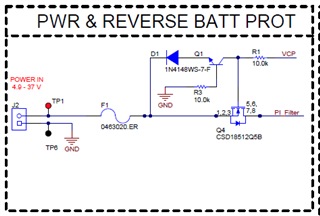

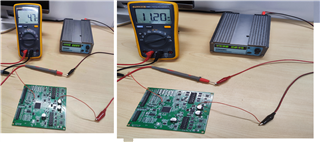

When the VCP is connected to Anti-Reverse Mos and the voltage is 10V and the VM is powered down, the measured voltage at the VM is 2V and the VGH is 0.

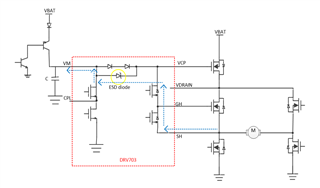

The voltage at the VM appears to be caused by leakage current inside the chip. However, according to the datasheet, there are two inverted diodes between the VM and the VCP, and the voltage on the VCP is theoretically not affecting the VM.

To avoid the effect of external capacitance, customer attempts to remove capacitance between VCP and VM, but there is still 2V at VM.

Could you please comments about the internal circuitry between VM and VCP? Since the VM has been powered down, is it possible that the voltage on the VCP can affect the VM's voltage through an internal circuit?

Thanks!

Regards,

Ivy