Other Parts Discussed in Thread: CSD18512Q5B, DRV8705S-Q1EVM,

Hello,

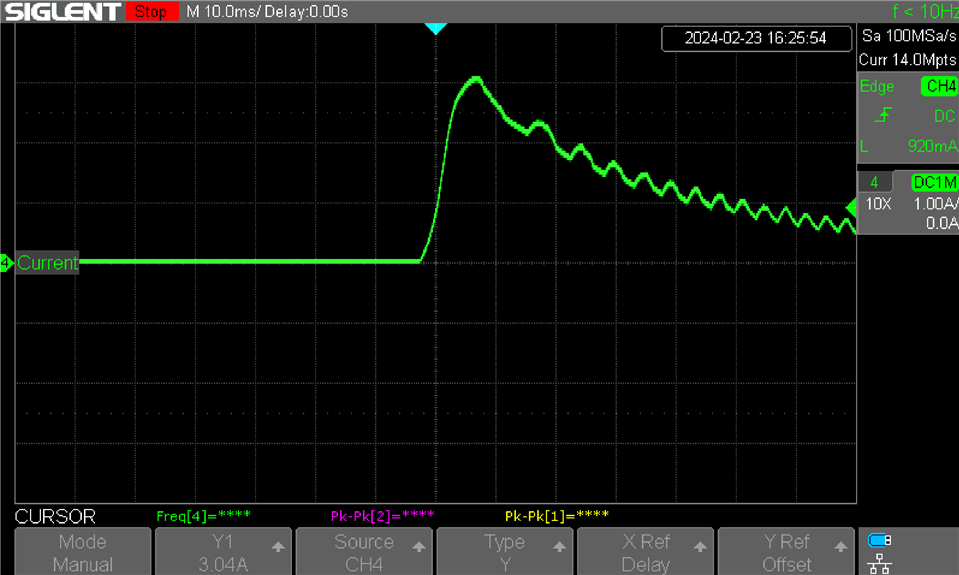

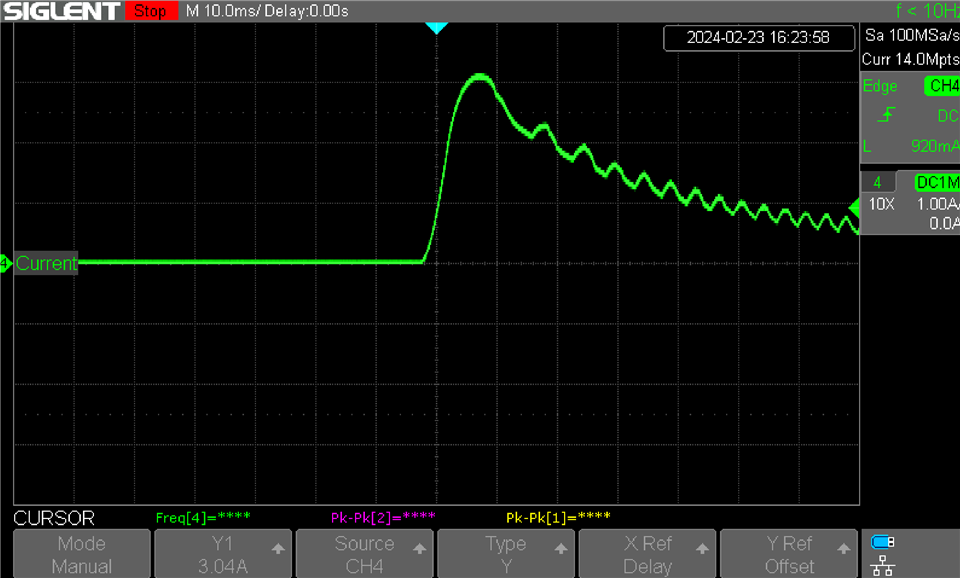

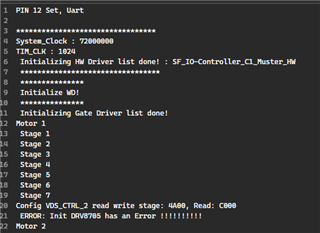

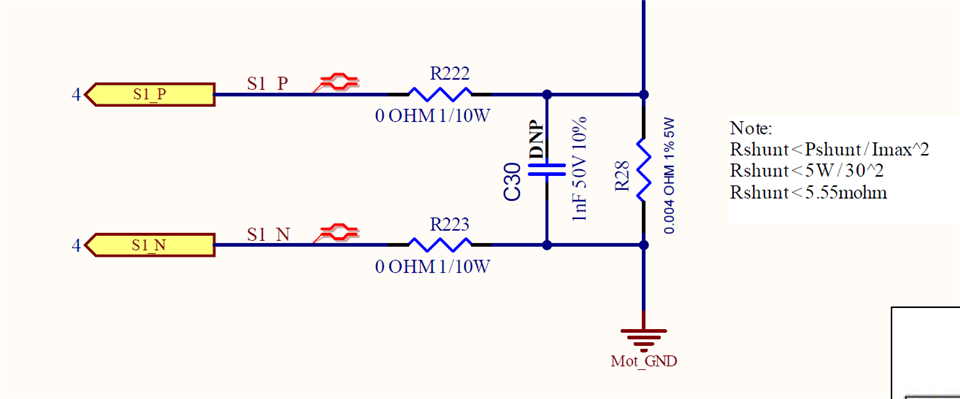

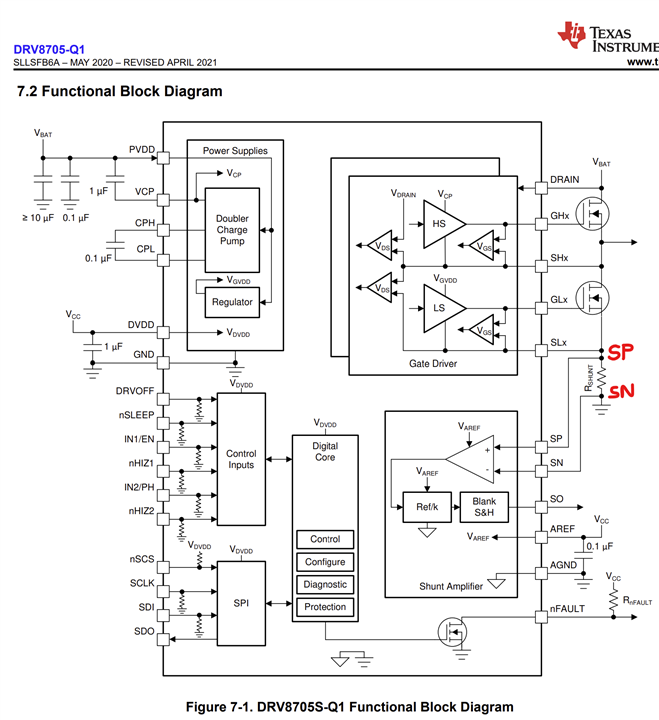

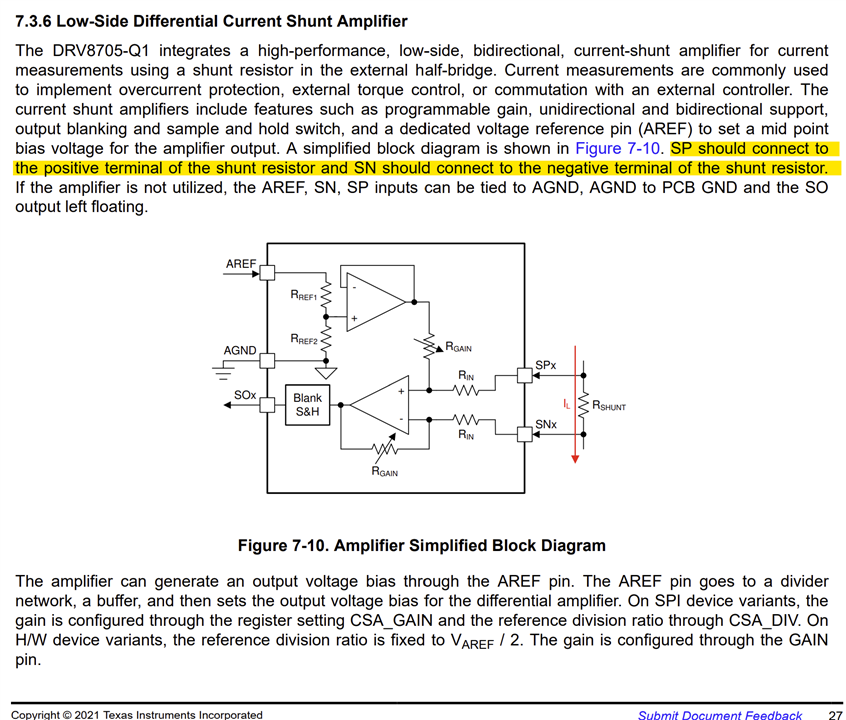

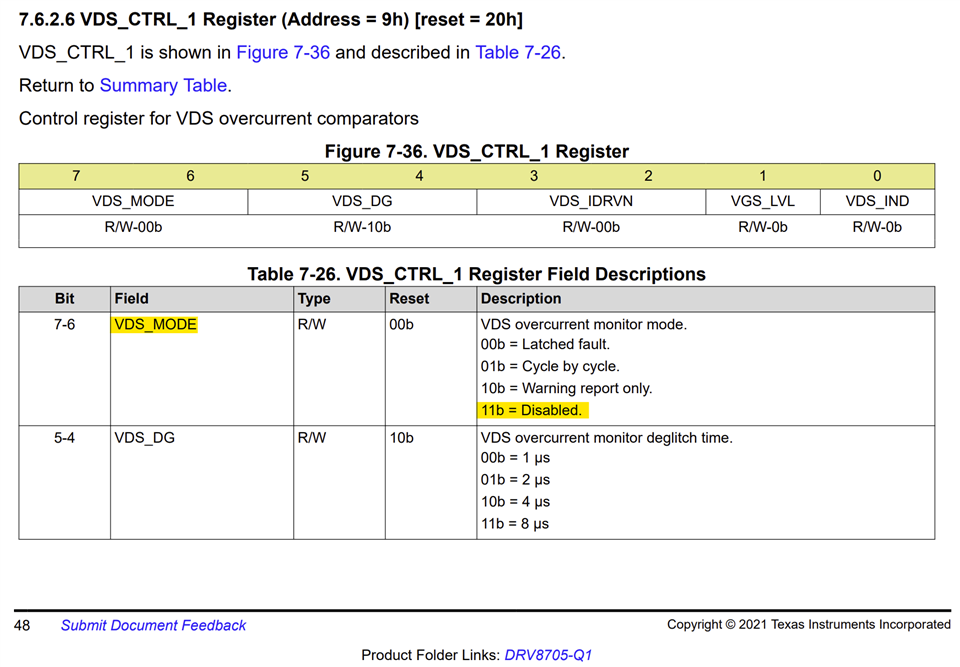

We are using the DRV8705SQRHBRQ1 motor driver in our application. Initially, we employed H-Bridge PWM Control, and the overcurrent fault was triggered correctly according to our current requirements. Subsequently, we switched to Half-Bridge Control for PWM mode, and after this modification, we did not observe an overcurrent fault. However, after adjusting the VDS overcurrent threshold, the overcurrent fault is now being triggered correctly

We want to know if changing the driver PWM modes affects the maximum current draw, or if there could be another reason for the change in the maximum current.