Other Parts Discussed in Thread: DRV8706-Q1

Hi,

I am using DRV8701 chip on the following schematics -

At connector A13 I am connecting a DC motor.

I have issue, when I use the motor, my nFault is going low. I want to fully understand why that happens.

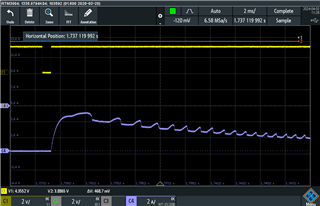

This is the scope of output current and nFault pin -

yellow is nFault

blue is current of the motor

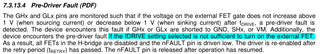

I can see it happens before the motor is consuming current. I wish to understand why that might happen and how to solve it.

thank you,

Michael