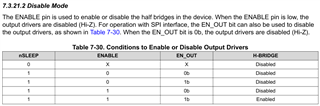

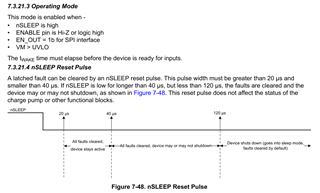

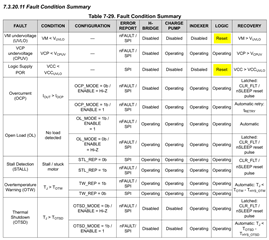

I am using the driver in spi mode. All pins are set accordingly to datasheet for working in SPI mode. SPI writes and reads normally the registers. I provide the step either by hardare pin or the software bit. In any case the problem is that after writing EN_OUT =1 that is 0x8F into register CFTRL1 , it turns automatically to 0. This occurs sometime after one step , sometimes after two step or maximum within 3 STEP .

Of course the motor does not turn or just has an initial pulse.

Can anybody help solving this mistery?