Other Parts Discussed in Thread: DRV8718S-Q1EVM

Tool/software:

Hi Team,

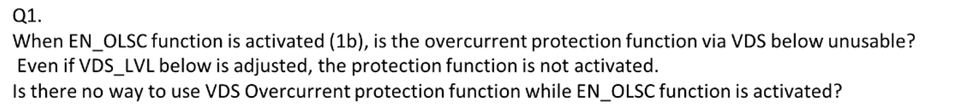

Please check the questions about EN_OLSC function of DRV8718-Q1 and let me know.

Regards,

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi Team,

Please check the questions about EN_OLSC function of DRV8718-Q1 and let me know.

Regards,

Hi Jeffrey,

Thanks for contacting us via this forum.

The EN_OLSC Offline Short Circuit and Open Load Detection function must be used only after disabling the drive using EN_DRV bit setting. The drive must be inactive or in other words "Offline". The over current protection function is necessary only while the device is in active drive mode in which case the EN_OLSC must be 0.

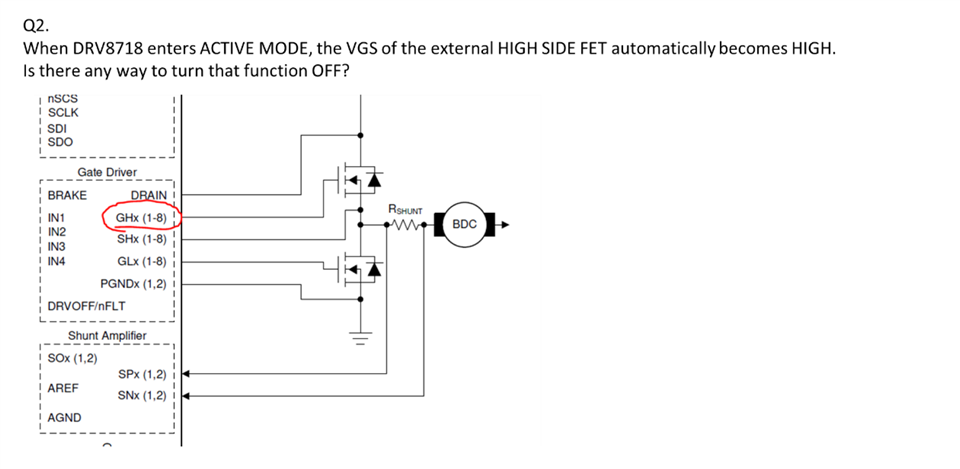

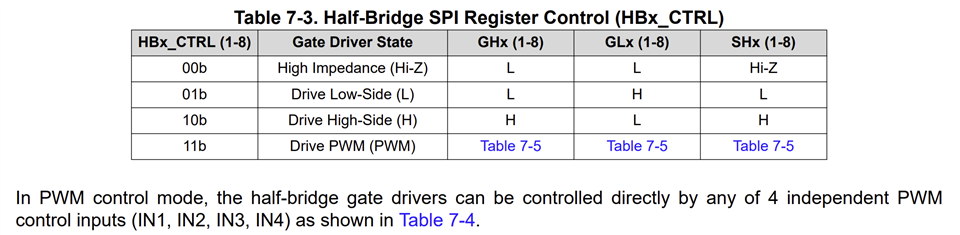

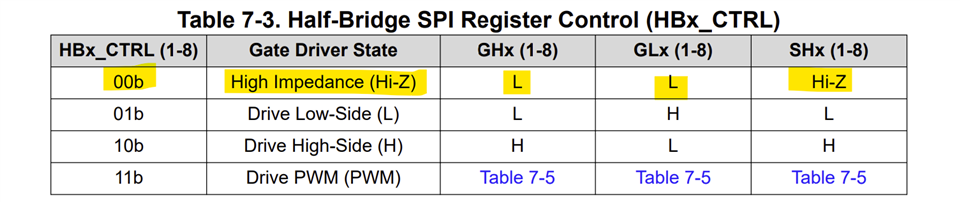

The GHx is controlled by the register control logic as shown in the datasheet - see below. Please ensure the GHx is not enabled before the device is set to active mode. Thank you.

Regards, Murugavel

Hi Murugavel,

Thanks for your response. Let me check it with customer and close or upload it if they have additional question.

Regards,

Hi Murugavel,

There is something wrong operation that different from datasheet when HBx_CTRL is 00b. Please check the attachment and test this issue with EVM. They want to know if there is a same issue with EVM. Please check it and let me know.

Regards,

Hi Jeffrey,

Let me test with an EVM and get back to you.

Regards, Murugavel

Hi Jeffrey,

I verified with a DRV8718S-Q1EVM. The Bridge control logic for HBx_CTRL 00b matches the datasheet description.

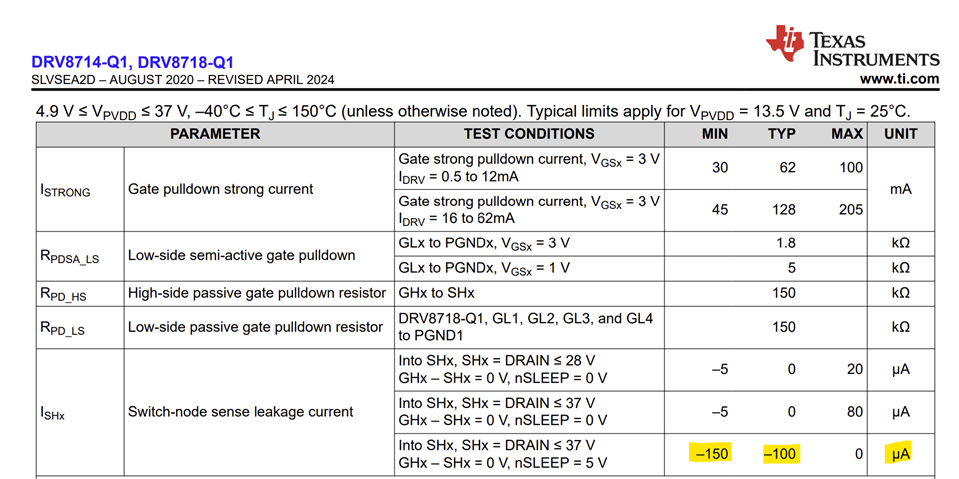

You'd measure a voltage slightly higher than PVDD on SHx and GHx. This is because of the low current leakage sink current into SHx, see below datasheet specification. If you measure the voltage across SHx and GHx it will be 0 V and the HSFET will not conduct with 00b configuration. If you connect a uA meter between SHx and GND you'd measure about 120 uA and at the same time SHx will be 0V. I have verified this to be the case as well. Thank you.

Regards, Murugavel

Hi Murugavel,

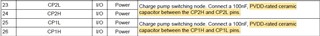

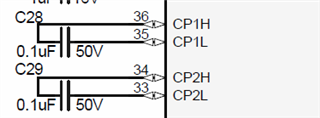

They are verifying their board with DRV8718 referring to your comment. During their verification, they found something wrong in the datasheet. It says that the rated voltage of ceramic capacitor between CPL2 and CPH2 is different from the datasheet below. Which one does it correct?

Regards,

Hi Jeffrey,

Please let me have the expert review this and give you a feedback. Thank you.

Regards, Murugavel

Hi Murugavel,

I'm sorry to push you, but please check it ASAP and let me know. Thanks for your support.

Regards,

Hi,

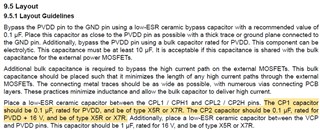

Thank you for your questions. There cap could have PVDD+16V. So normally ~50V cap is used as TI EVM. 9.5 sentence is correct.

regards

Shinya

Hi Shinya,

I think that all CP1 and CP2 capacitors should be rated for PVDD+16V. Is it correct? If yes, please let me know why there is the different rated description in the datasheet between CP1 and CP2.

Regards,

Hi,

Yes, CP1 and CP2 keep same. Simply we recommend to use 50V cap for CP1 and CP2 same as EVM.

regards

Shinya Morita

Hi Shinya,

Thanks for your clear answer. I will close this case. I appreciate your support and Murugavel's support.

Regards,