Hy

My First Time Design Questions are:

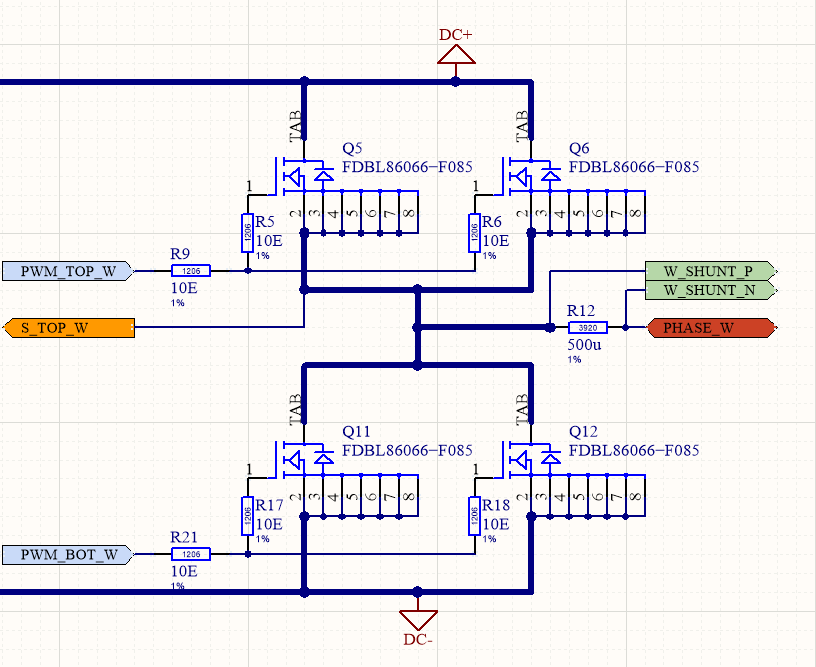

1. Is it possible to place two MOSFET's in parallel? (See attached schematic screenshot of on Phase Leg)

2. The thermal information are confusing. What is the maximum power dissipation of the gate drive section?

The conditions are: Tamb= 75°C, fs = 12kHz, Vgs = 15V Qgmax = 180nC (2xQg of 90nC), Independent PWM Mode, Space Vector sinusoidal control

3. "Standard" applications requires a gate resistor for each MOS. Is this also true for the DRV8353R?

4. Is it possible to use the internal current shunt amplifiers in a "phase current configuration" instead the "leg current configuration"

5. Is Figure 33 the only dead time insertion mode?Can we disable the dead dime feature?

Kind Regards

Rolf Lerch