HI team,

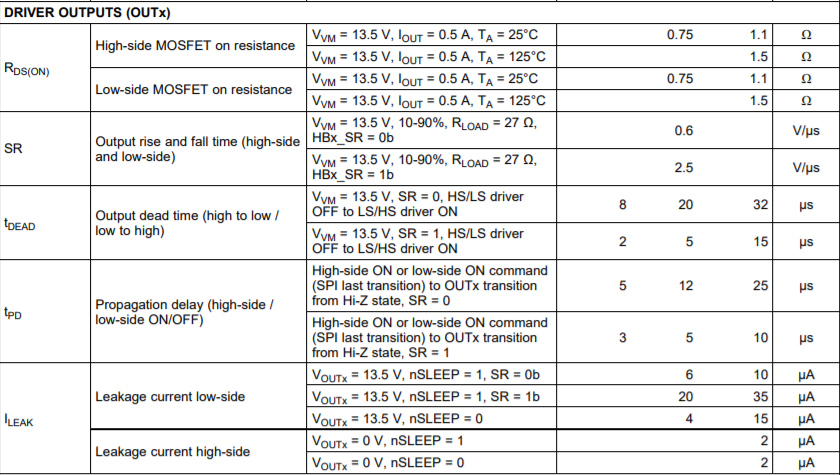

My customer is using the DRV8906 now. Here we want to use two channels to be parallel to achieve higher current level. But not sure about the channel to channel delay( The chip to chip delay is several us. Whether it will cause one channel overcurrent because the on time miss match?) Thanks.