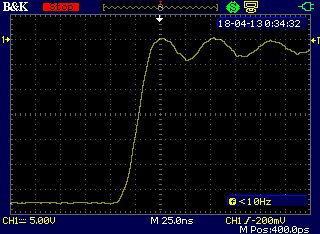

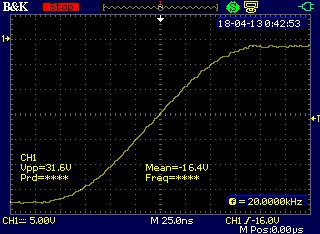

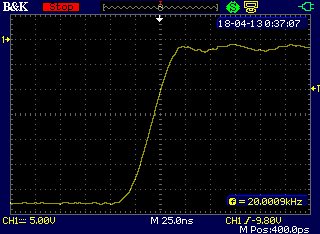

No load connected with proper threshold settings and yet over current faults chatter at the digital output. Increased the threshold but had minimal effect. Dead time is large and increasing it is not helping much either. What could be wrong? When the function is only disabled, it works fine. There are 10Ohm gate resistors.

Thanks.