Hello TI team,

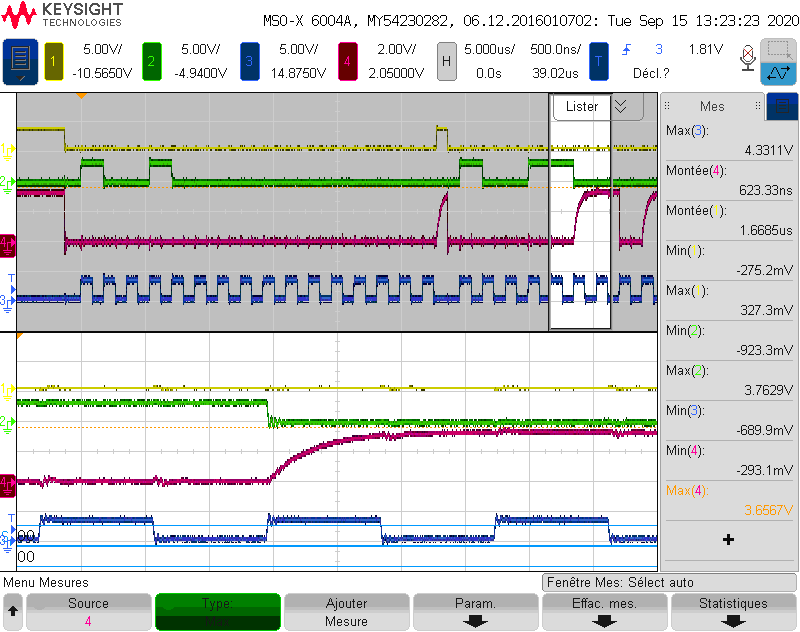

We are using the SPI interface to communicate between our microcontroller and the gate-drive DRV8323S. We followed your hardware recommendations described in the datasheet by using only a 10k pull-up resistor connected to the SDO pin. We record a slow rise time on SDO around 600ns.

There's no capacity in parall. What's your opinion?

Channel C1 : Chip Select

Channel C2 : SDI

Channel C3 : Clock (560kHz)

Channel C4 : SDO

Pierrick Ecoeur

pierrick.ecoeur@sonceboz.com