Hi,

I have a few questions about the SPI Parity Mode transfer configuration and behavior for TPIC71002-Q1. We're using 2-frame or 4-frame SPI Burst Transfers.

- Datasheet says that "Device supports parity check during Address Mode Transfer." (page 24), but on the next page it says that parity detection results in actions (like setting parity error flag) which "are performed either if the parity failure is detected in the Address Phase or the Data Phase"

- While testing it seems that parity checks are done on both address and data phase, but I want to confirm this with you. Are parity checks done during both address and data phase of transfer?

- "The device responds with forced parity error during Data Stage (next SPI transfer)."

- What exactly is meant by forced parity error? Is it some data sent with wrong parity bit set on purpose, or what is it?

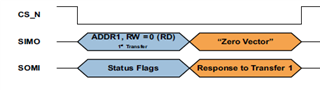

- If I enabled parity mode and am using 18-bit SPI transfers ( [8-b address + 1-b address parity] [8-b data + 1-b data parity] ) like the example below, and parity error happens during ADDR1 phase, when should this forced parity error be received by the master? Should it be right after ADDR1 phase in "Response to Transfer 1" or in the next transfer?

- In which Inhibition Mode should the device be when enabling parity mode?

- When device is in IM1, first SPI transfer after enabling parity mode results in data with wrong parity bit being returned during address phase ("1101 0000 x", where x is parity bit and is opposite to correct value regardless of if parity mode configured is even or odd). Is this ok? This doesn't seem to happen on the first SPI transfer after enabling parity mode while device is in IM0.

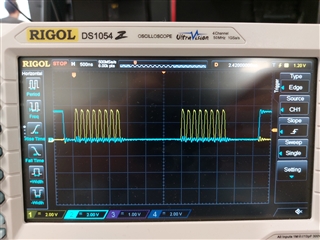

- Why does SPI_ERR flag get set and is read during Device Status phase if previous SPI transfer was Read with Zero Vector being sent after the Address Phase (see screenshot above)? I spoke to a colleague of mine who already contacted you about this issue and he got the answer that this error can be ignored, but can this somehow be remedied so that this doesn't happen?

Best regards,

Tomislav