Other Parts Discussed in Thread: UCC21732QDWEVM-025

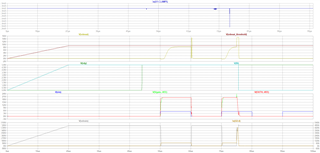

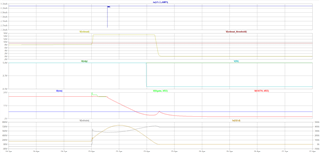

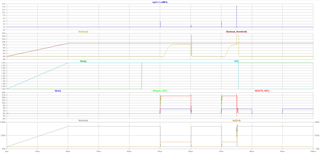

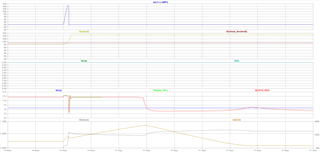

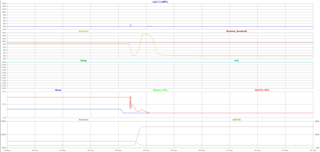

(1) I have been running a simulation in LTSpice evaluating the UCC21750 gate driver and require feedback with the waveforms I'm seeing. I'm seeing oscillations during turn-off and it would appear that there is some correlation with previous posts occurring the same fate of actual devices. We are in the process of purchasing the UCC21732QDWEVM-025 to evaluate this family of gate drivers to determine whether this is a suitable gate driver for our application.

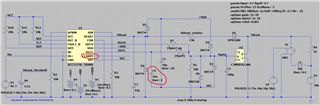

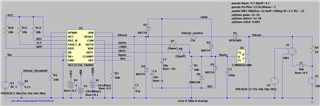

The simulation is as follows.

- 50kHz signal starting at 50us with 50% duty cycle.

- CREE C3M0016120D silicon carbide MOSFET used as the switching device (spice model provided by CREE).

- short circuit applied at 75us to test the soft turn off during a desaturation event.

- 700VDC bus voltage.

- resistive load of 10 Ohms.

(2) The STO of the UCC21750 has an internal 400mA current source which is a little restrictive for our application. I have added an RC network to the simulation to vary the STO time which was recommended by TI when using a buffer circuit to enhance the current drive capability. The simulation appears to function correctly with the RC network however, I would like confirmation by TI that it's acceptable to use the UCC21750 in this fashion? It functions better when the active clamp circuitry is disabled.