Dear Sirs,

Please refer to attached for customer schematics.

While customer testing Aux power input and found questions.

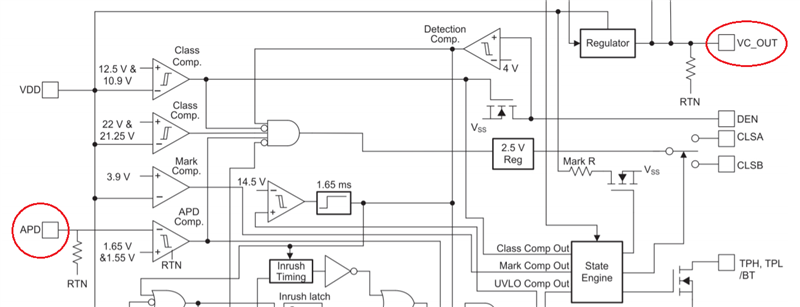

1. When APD input is higher than 1.65V, and VDD input from DC27V~DC41V, there is output from VC_out.

If APD input is below 1.65V or floating or 0V, the VDD needs higher than 41VDC then the VC_out starts to output voltage.

Is that normal or not?

2. What is the relation between the APD and VDD since there is no detailed information in datahseet.

As function block, there is no any direct trace for control between them.

Thanks.