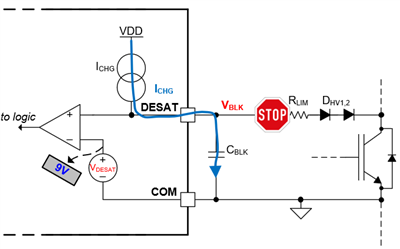

For SiC driving, we need faster short-circuit detection time!

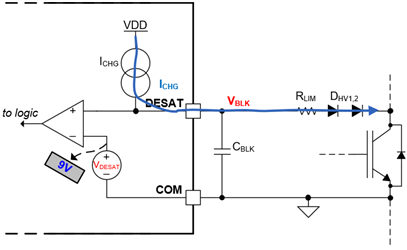

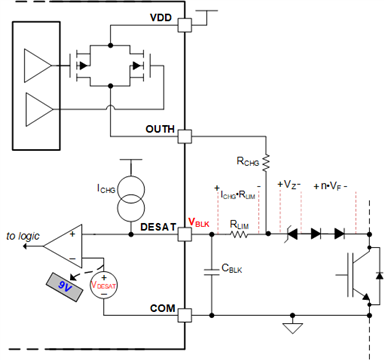

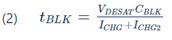

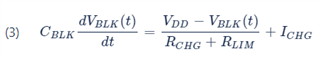

This value is dictated by the value of the blanking capacitor and the fixed internal DESAT charging current (500uA)

How can I have FAST SC-detection time with DESAT without choosing an unfeasibly small value blanking capacitor, so that I can safely design smart gate drivers with DESAT detection for SiC applications?

Parts with DESAT detection include: UCC21710, UCC21710-Q1, UCC21750, UCC21750-Q1, UCC21759-Q1, ISO5451, ISO5451-Q1, ISO5851, ISO5851-Q1, ISO5452, ISO5452-Q1, ISO5852S, ISO5852S-Q1, ISO5852S-EP, ISO5500