Other Parts Discussed in Thread: AM5716

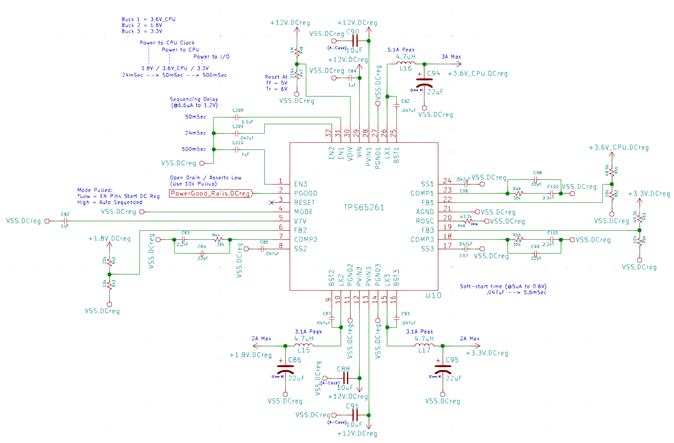

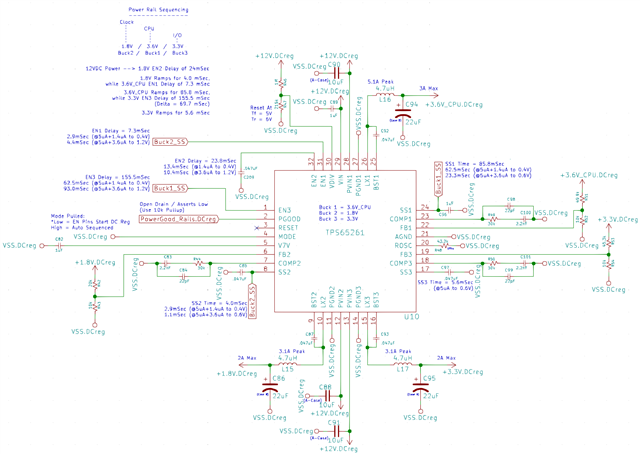

I am using the enable pins to sequence the startup of the three supplies for my application using an external capacitor charged from the internal current source. It works perfectly to delay each supply, however I have noticed that the capacitors remain charged for quite a long time after removing power. The result is that the supplies are not properly sequenced after a recent power off. Is there a suggested circuit or method to discharge these caps reasonably quickly after power off?

Thank-you!

-Jason