Other Parts Discussed in Thread: ISO5452

Hi Ti,

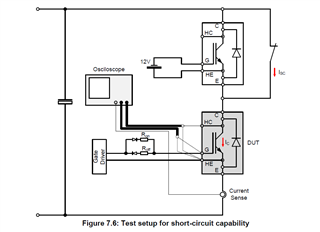

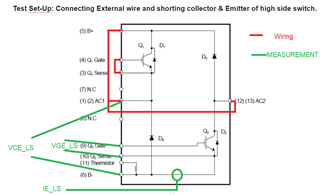

I am performing short circuit type -1 test based on AQG324 standard. I am using an external wire to short the High side switch and using a function generator to give gate pulse to the bottom side switch.

I am using ASPM16 Power module from Onsemi with the following modification

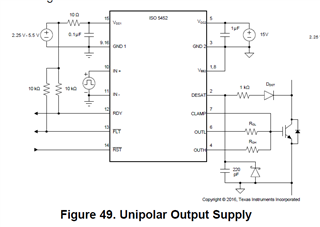

I am using ISO5452 gate driver IC from TI for providing the gate pulse to the bottom switch. The gate driver design used is similar to unipolar output supply suggested in datasheet under chapter 10.2.2.1. For this test i am using isolated power supplies for VCC2.

The RGH value is 8.25 ohm and RGL is 1.55 ohm.

A Signal is provided from Function generator to low side gate driver Pin 10 (IN+) of ISO5452QDWQ1 Driver IC, which is getting disrupted while performing the short circuit test at a bus voltage of 40v and higher, due which there is a false turn on & Turn off of power module.

In the above Image, Green waveform is the Non-inverting gate drive voltage control input. Blue waveform is the Positive gate drive voltage output. Yellow waveform is gate emitter voltage (after gate resistor) at the IGBT gate pin. Red waveform is the collector emitter voltage of the IGBT.

Request you to provide suggestions to mitigate this issue.