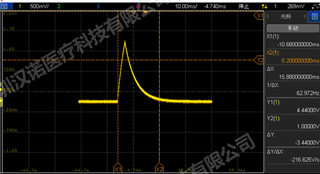

There is an abnormal behavior on our circuit,and the phenomenon is not easy to reproduce。

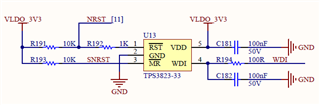

Currently we set WDI to high-impedance , we purpose to disable the WDI timer from our system.

I found the problem of adding capacitors in the forum,but I don't understand how WDI judges the correctness of pulse signal

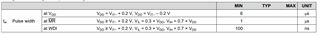

According to the specification

Q1: Which it will generate its own WDI pulse to ensure that RESET does not assert.

Do these signals also conform to the parameters in the table?

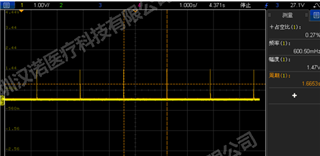

At this time, use an oscilloscope to measure whether the WDI signal is correct

Q2: How the chip judges the WDI signal and What parameters need to be met?

Q3: As shown in the schematic diagram, if WDI is not used, Is there any hidden danger in the circuit?