Other Parts Discussed in Thread: TPS54386

Hello

Regarding the TPS54386-Q1, the buyer is requesting a response from the supplier.

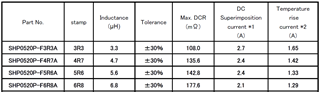

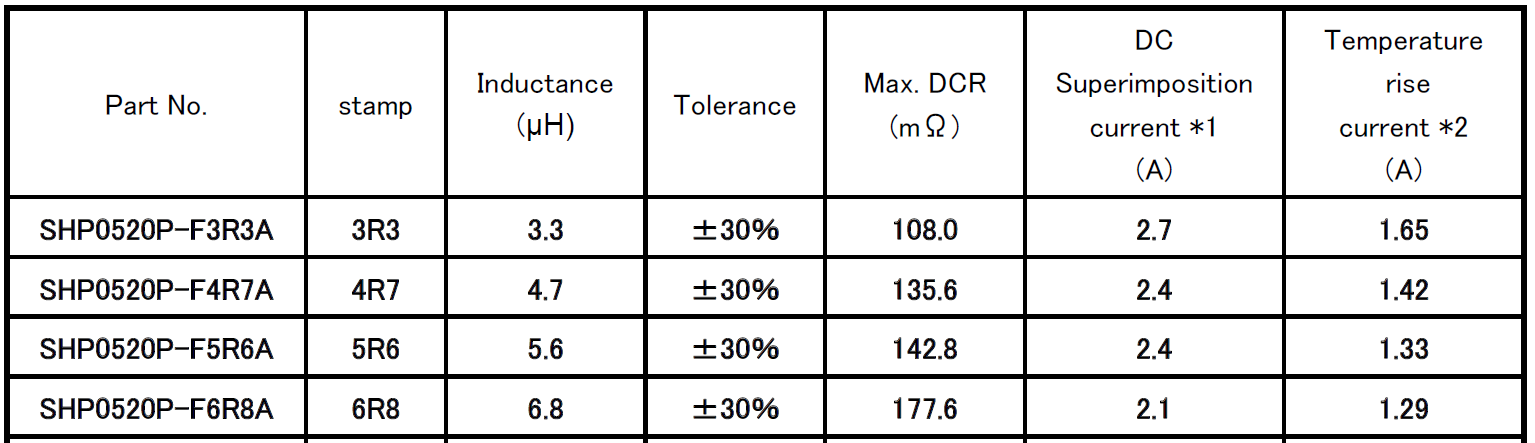

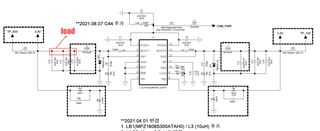

Currently I am using 3.3V output for SW1 part.

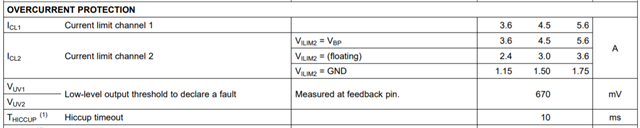

During the load test, when a load of about 1.6A is input to the 3.3V line, the protection circuit works when the voltage drops to 2.8V, and it was confirmed that the two channels enter the protection state.

There is a question about why the protection circuit operates at 1.6A when the maximum available current is 3.6A.

I explained that the TPS54386 IC detects and operates an externally input load, but the buyer does not understand.

Can you answer this question?

thank you.