Other Parts Discussed in Thread: AM6442, TPS745,

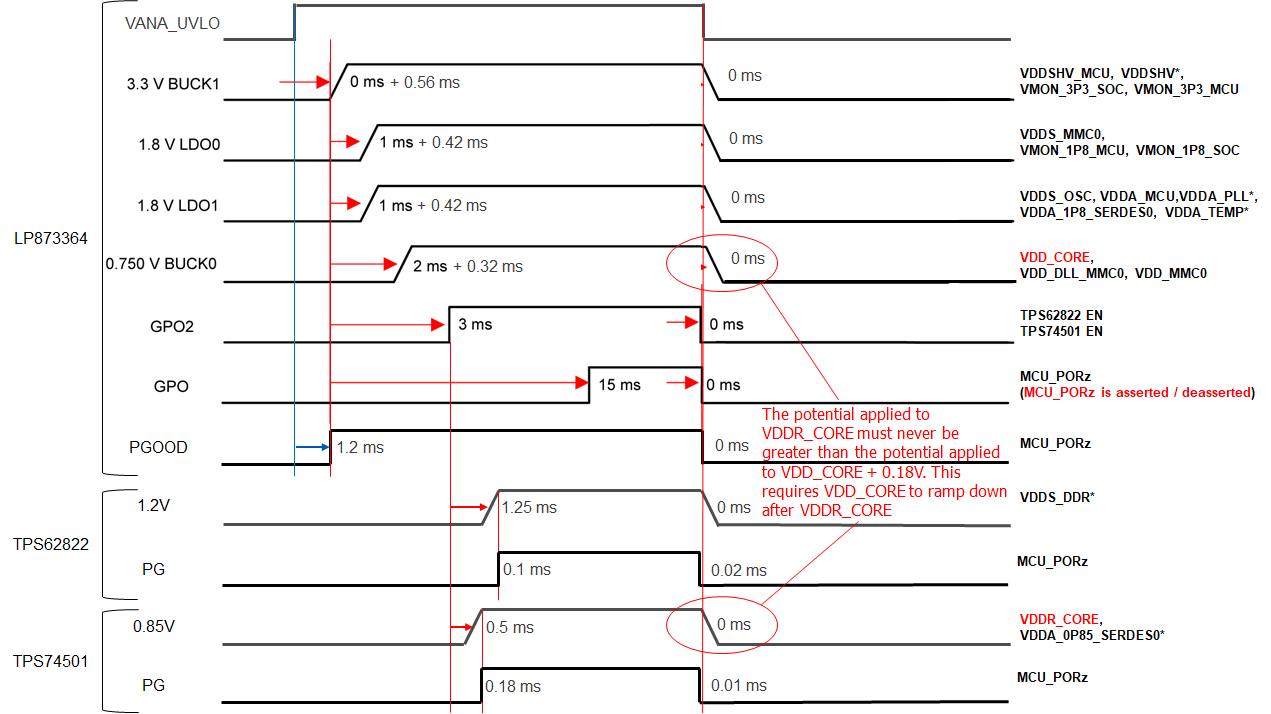

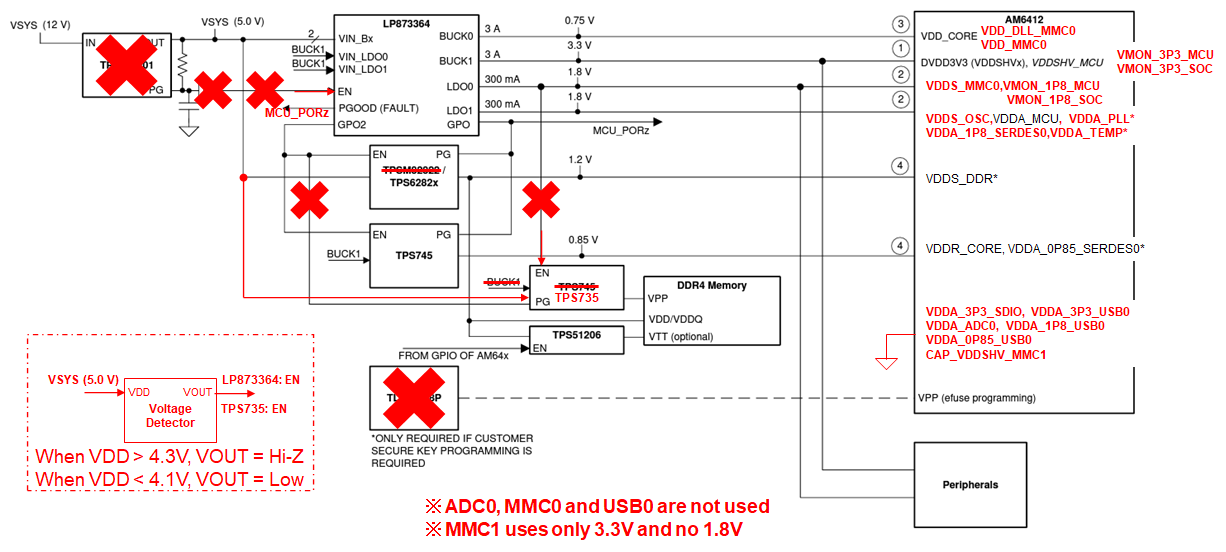

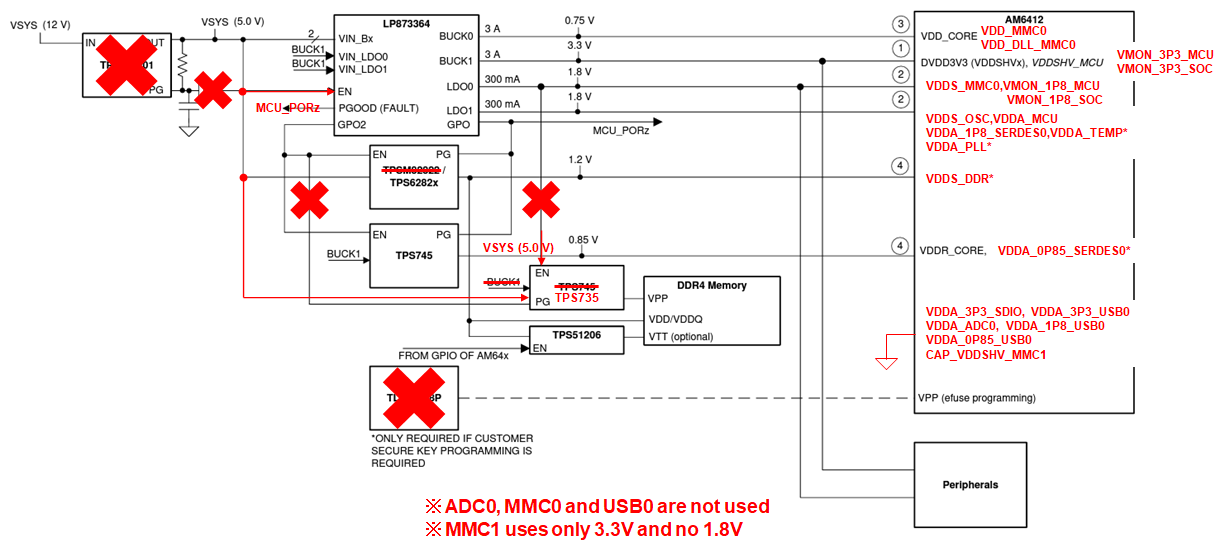

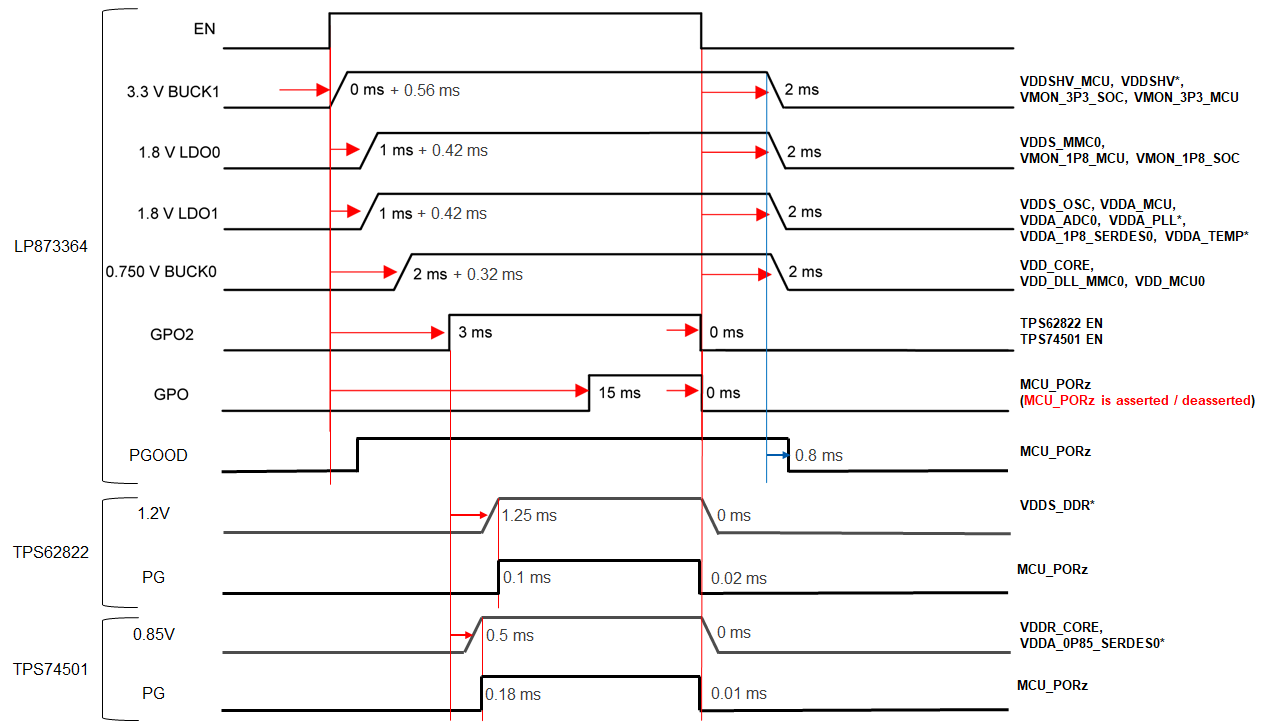

Our customer is designing a prototype board with the AM6442 SR1.0 and powering the AM6442 with the LP873364.

Can the EN pin be connected to VSYS (5V) along with the VANA and the VIN_Bx power pins? If not, how should the EN pin be connected?

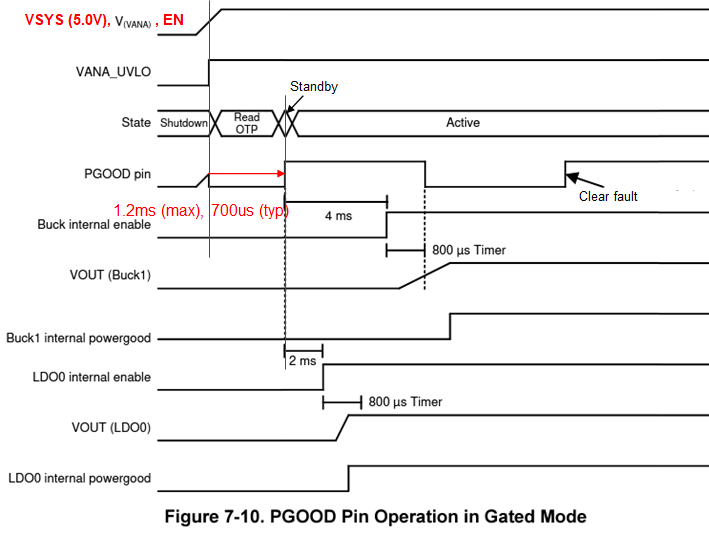

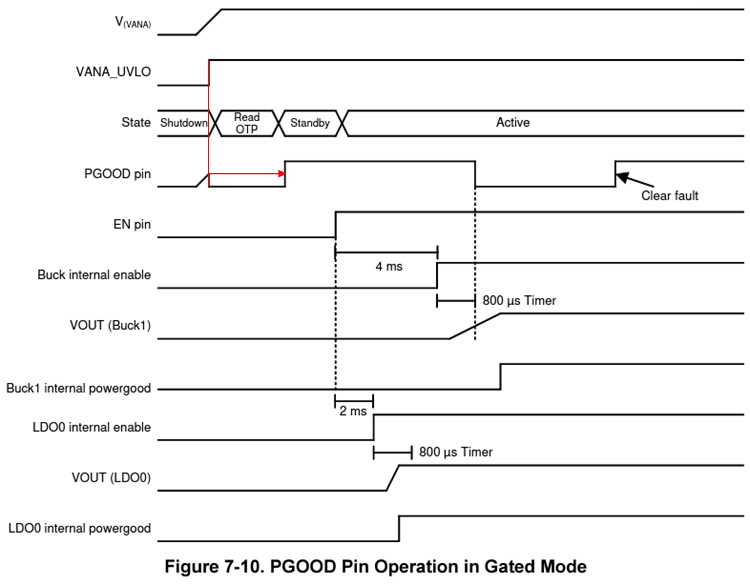

PGOOD is set to active or asserted state upon exiting the OTP configuration as an initial default state.

What is the delay between the V(VANA) voltage being above the VANAUVLO threshold level and the PGOOD pin being asserted?

Our customer connects the PGOOD pin to the power-on reset pin (MCU_PORz) of the AM6442 along with the GPO pin and other power supply PG pins.

Does this connection work correctly to power-on reset the AM6442 both under normal and fault conditions? If not, how should the PGOOD pin be connected?

Best regards,

Daisuke