Other Parts Discussed in Thread: TPS563202EVM

Hi,

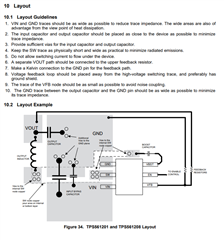

on the SPEC in section 10.1 it is recommended not to route the switching under the device.

can help to elaborate more why it is not recommended?

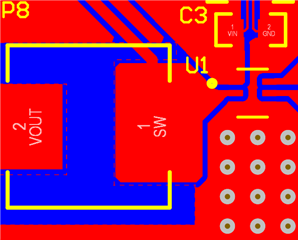

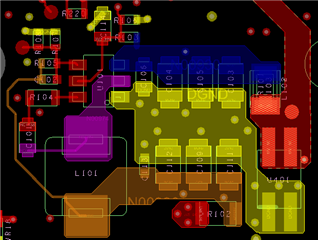

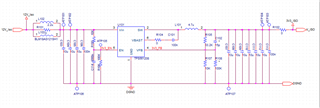

in my design i've routed it beneath the IC to minimize the SW line and not to route it with VIAs in more than one layer:

SW - purple, GND- yellow, Vin - Blue, Vout - Orange

can help to review layout and advise how crucial it is to fix?

have to say that design was checked (@ -40C, @25C, @105C) for ripples, current transients, wake-ups, efficiency, load regulation, voltage regulation - no issues found.

Thanks,

Uri