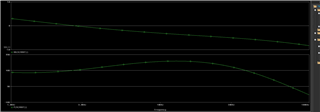

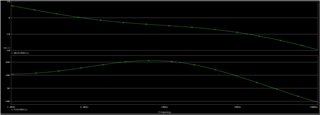

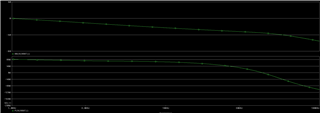

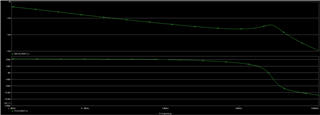

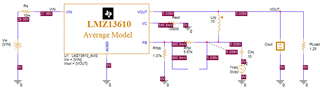

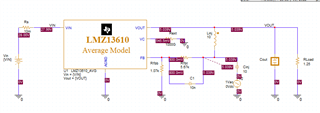

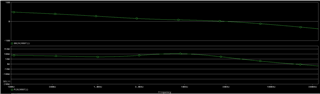

I am using the PSPICE average model to understand the stability of my design. i am running 28V in, 5V out, 1.25ohm resistor for a load of 4A. To be consistent with the datasheet graphs, I am using x2 330uF (tantalums), x1 47uF ceramic, and x1 0.01uF ceramic. Based on this, I get a phase margin of ~46deg at a crossover frequency of 3kHz. I am trying to find ways to increase the phase margin. Decreasing the capacitance will help as long as I can still meet my load transient and tolerance requirements. I have also found that increasing the ESR for the 330uF tant, will also help.

Are there any other ways or suggestions for increasing phase margin? Is it typical for the part to be somewhat low for minimum capacitance per the datasheet?