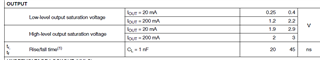

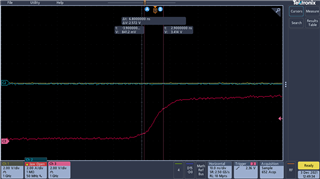

My question deals with the output stage of the UC1823. I am using the UC1823 output to drive drivers that are 5V input rated. So I am running the 5V VREF voltage into the VC pin and getting good results in the lab with it driving all the way to 5V with a good fast rise time between 0.84V and 3.4 V of only 6.8nsec. So I don't understand the 2V typical saturation voltage. That seems really high for a BJT totem pole stage. What does this driver look like. Can I reliably drive a 5V gate driver as I have been?