Other Parts Discussed in Thread: LM5143

Hi team,

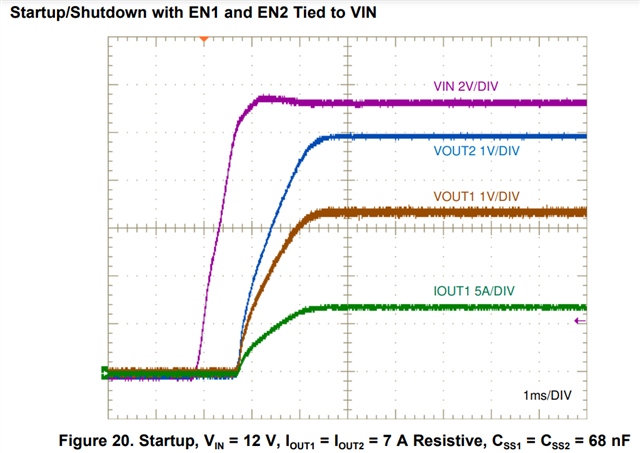

In our LM5143EVM,there is a start-up characteristic showing as following:

With the Css=68nF setup, the calculated soft start time should be 1.94ms, but I am little confusing about the 1.9ms time division.

In above waveform, there is a no swtiching stage after Vin is over UVLO threshold which is 0.9ms roughly; and then the output voltage rising stage is 1ms;

So what is the first stage for? And the calculated SS time is usual the stage 1 + Stage 2 Vo rising, if this understanding is right?

Thanks.

Best regards

Mia Ma