Hi,

Customer is encountering issue regarding this IC, please see details below.

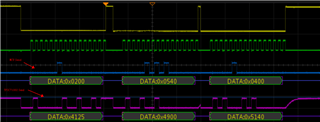

When SCLK is normal and parity is not enabled, SPI_ERR is not reported every time the register of TPIC71002 is read or written. As shown in the figure below, when I read the ID register for the first time, the SPI_ERR flag bit returned by TPIC71002 is 0, and then when I write to the STAT register, the SPI_ERR flag bit returned by TPIC71002 is 1. When reading the STAT register SPI_ERR is 0.

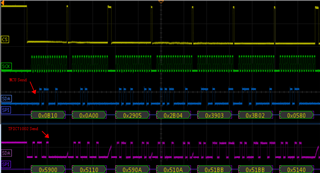

Through the operation of the above steps, the TPIC71002 is in the IM1 stage at this time, and after 2ms, the following operation is performed: 1. Write the DAC register, the SPI_ERR status returned by TPIC71002 is 1. 2. Read the DAC register, the SPI_ERR status returned by TPIC71002 is 0. 3. Write the ZCNT0 register, the SPI_ERR status returned by the TPIC71002 is 1. 4. Write the ZCNT1 register, the SPI_ERR status returned by TPIC71002 is 0. 5. Write the T0CNT0 register, the SPI_ERR status returned by TPIC71002 is 0. 6. Write the T0CNT1 register, the SPI_ERR status returned by TPIC71002 is 0. 7. Write the STAT register, the SPI_ERR status returned by TPIC71002 is 0. 8. Read the STAT register, the SPI_ERR status returned by TPIC71002 is 0.(The waveform picture corresponding to this bar is not displayed.)

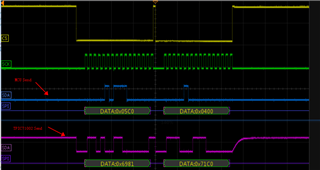

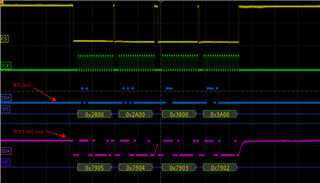

Through the operation of the above steps, the TPIC71002 is in the IM2 stage, and after 2ms, the following operation is performed: 1. Write the STAT register, the SPI_ERR status returned by TPIC71002 is 1. 2. Read the STAT register, the SPI_ERR status returned by TPIC71002 is 0.

Besides TPIC7100x, are there any more detailed information or routines available? Or some considerations when using the TPIC7100x.

Thank you in advance.

Regards,

Maynard