Other Parts Discussed in Thread: LM10011, INA226

Dear TI Team,

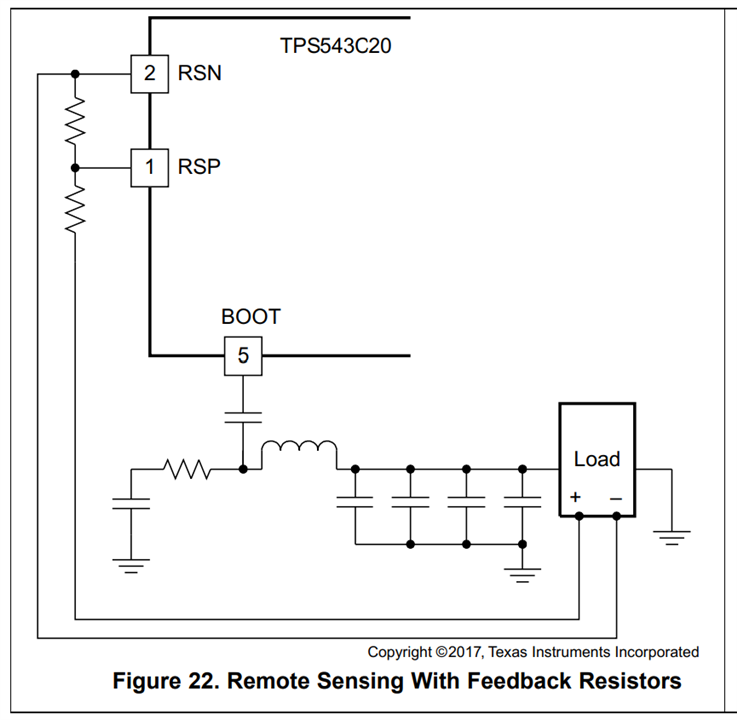

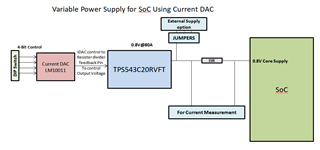

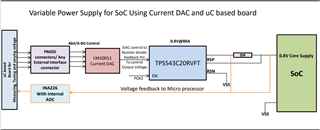

We are using TPS543C20RVFT ( 2 Phase stacked Configuration for 80A ) IC in our design. This is used for supplying 0.8V core supply of our major SoC chipset. During PI transient simulation we found that the chipset may produce 130-140A high current transients in the duration of 1ns - 10ns.

1. In this case whether IC will be able to handle such high transients.?

2. What is maximum transient that the IC can handle ( 2 Phase stacked configuration ) ?. As per one of our earlier discussion its been told that 120A can be handled by stacked 2-Phase configuration ( 60A each ). In this case what is the maximum pulse width/the transient time with 120A that IC can withstand.

3. If TPS543C20RVFT IC is unable to handle such high transient currents, then what will happen for the IC if such high transient is been introduced by load. Will it go to over current protection state and blank out or IC will go bad.

4. How much minimum decoupling capacitance should be provided on the board to handle such high surge currents in VRM. Please provide your input for the same.

Best Regards,

Vyshnav Krishnan