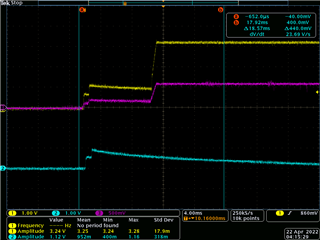

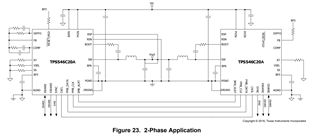

I have a design in which I have two separate supplies using the TPS546C20A to produce +1.2V and +0.8V. I haven't turned on the +0.8V supply until I understand the behavior of the +1.2V supply. I captured a waveform on my oscilloscope that shows the +1.2V supply coming up to +1.2V....then ~8ms later, it jumps to +3.3V. In my design, I have the VSEL pulled up with a 10K ohm resistor to BP3. Then, I have two 10K ohm resistors connected from DIFF0 to FB...and FB/DIFF0 to GND to produce +1.2V. I measure the 0.6V at the FB pin as I expected...then did see a +1.2V at one of the 10k's. What would cause the output voltage to be overridden from +1.2V to +3.3V?

Thanks,

Jeffrey McCasland