Hello,

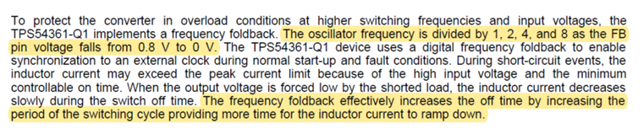

I guess the output current of a TPS54361-Q1 supply circuit will be reduced when the output is shorted to GND because of the TPS54361-Q1's switching frequency foldback function, but how small can the output short-circuit current be when the load is ideally 0 Ω?

When a short-circuit event happens, I guess the switching frequency is decreased to one eighth (1/8) and the duty cycle is reduced to its Min on-time, but how much can the output short-circuit current be, in other words?

Best regards,

Shinichi Yokota