- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

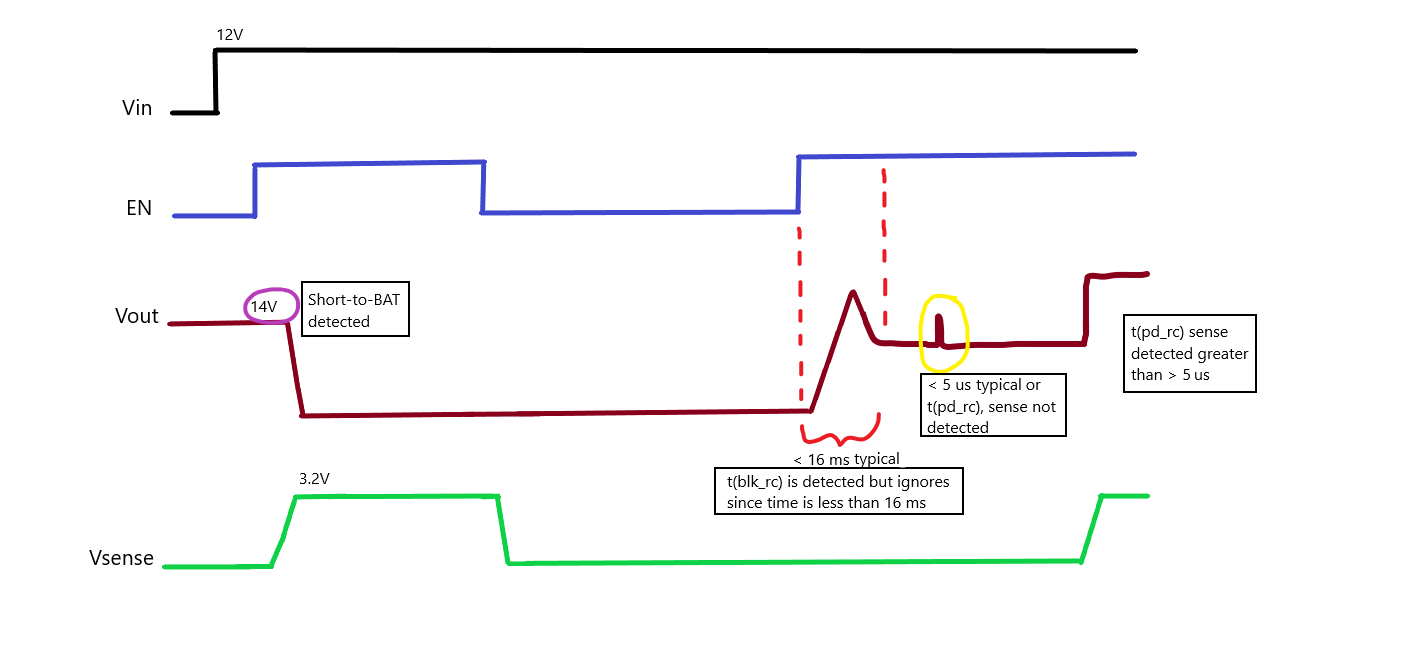

Wants to understand what is definition of below spec in D/S.

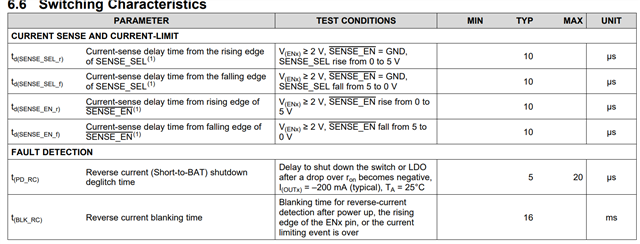

For things like td_sense_en_r, what does it mean?

For delay time of tpd_rc, what does it mean? Cannot really understand the test condition. Would you please give me a diagram to illustrate this?

-A

Hey Albert,

td(sense_EN_r) is the delayed time that it takes for the td to start to rise.

For t(pd_rc) this is the reverse current shutdown deglitch time once there is a fault detection. This was tested using I(outx) = -200mA (typical) with Temperature ambient = 25 degrees C.

Let me know if you have any other questions.

Thanks,

McKyla

Hi McKyla,

Thank you for your reply. Is my understanding below correct?

1. t(pd,rc) is the deglitch time that from "current through pass FET becomes negative, or STB is detected" to "device shuts down".

2. When "current through pass FET becomes negative, or STB is detected" only lasts below t(pd,rc), the device would not shut down and will thing this reverse current is just a glitch.

-A

Hey Albert,

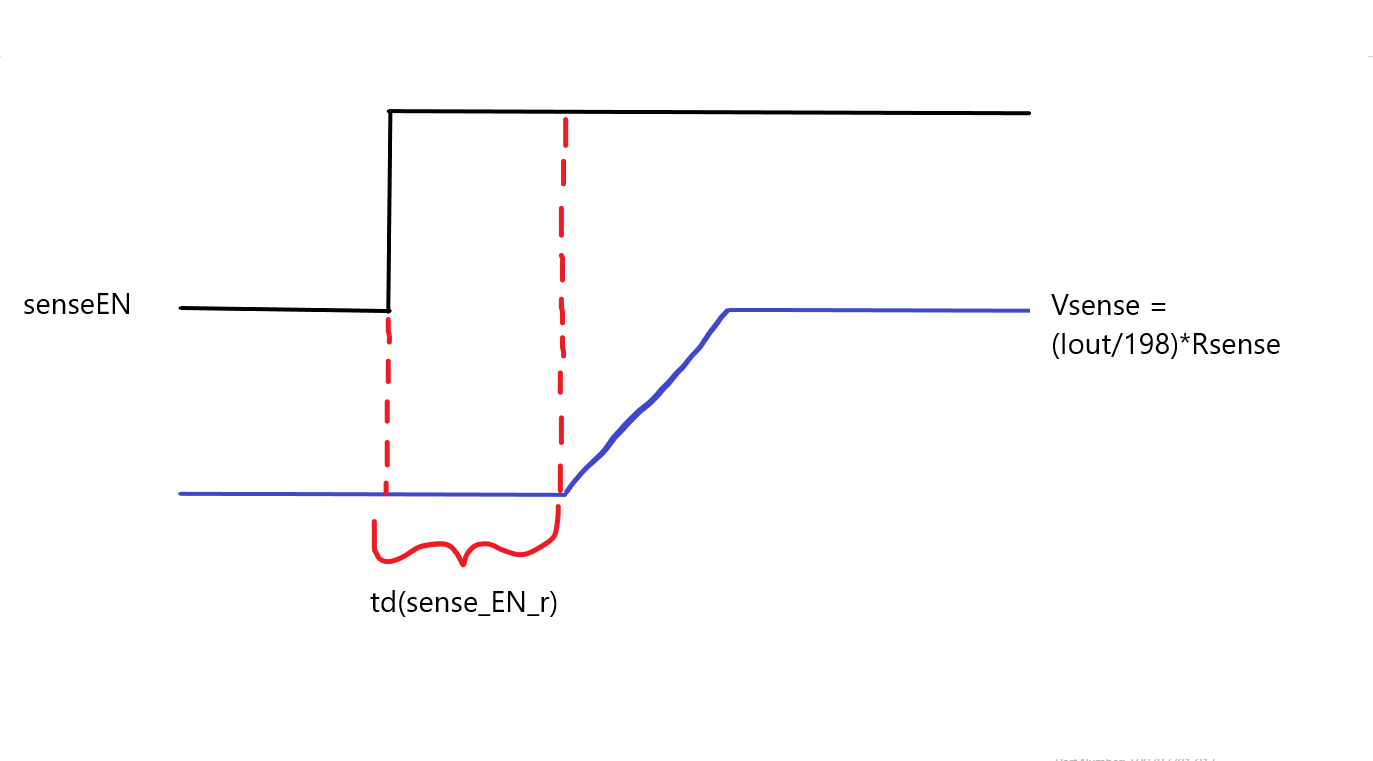

There are three different variables(short-to-BAT or V(stb_th),t(pd_rc), and t(blk_rc)) that can be tripped at different times. Please see below image to help explain.

V(stb_th) or short-to-BAT is tested when the EN is in turnon sequence. If the voltage is above 110mV (range specified below), this will go into shutdown. The fault circled in purple shows when this would happen.

t(blk_rc) is reverse current blanking time when the ldo is rising. In the example below the output overshoots, but less then the typical 16ms. The t(blk_rc) will not trigger a fault. However, if the ldo was to overshoot in greater then 16ms then this would cause a fault.

The t(pd_rc) is the time delay that the ldo can "misbehave" and have reverse current before going into shutdown. If time is less than 5us typically, then this will not cause a fault (as shown in yellow), but if the ldo was to go high for a longer period of time this would cause a fault.

Hope this helps!

McKyla

Hi McKyla,

Thank you for your reply. I feel sorry my so many questions have bothered you:). Just one question here.

In terms of STB, the purple area actually means when VOUT-VIN<=V(stb,th) and device is in turn-on sequence, STB is triggered and FETs will be shut down. There is one point I am confused. Even though 7702 detects VOUT is short to battery and it turns off its internal FETs, when VOUT is already short to battery, the FETs have nothing to do to prevent current flow from VBAT to VOUT because device is already short. How could 7702's VOUT after STB falls down?

-A

Hey Albert,

No problem.

Yes, you are correct on VOUT-VIN<=V(stb,th). For the image below, usually the Vout is not shorted locally like this to the Vin. However, if this did happen the Vbat usually has a diode before the Vin to prevent this current flow in this module. I believe you are asking about when Vout is in fault mode from STB when will the device regulate again? If so, the device will regulate again once the EN is triggered.

Let me know if you have any further questions.

Thanks,

McKyla

Hi Mckyla,

Could we support STB when device is in normal regulation? Why does the device only support STB detection in turn-on sequence?

-A

Hey Albert,

It checks in the beginning to make sure there isn't a short when powering up. It then will ignore some ringing or overshoot in the beginning while powering up during a short period of time. If a STB happens later on the t(pd_rc) will caught it if it has reverse current flow. While t(pd_rc) and STB are different, they are usually related and in most cases STB is how the t(pd_rc) will be trigger. While this does not always have to be the case, if there is reverse current flow during this period from a STB the ldo will turn off.

Thanks,

McKyla