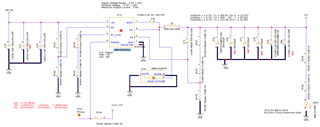

The following circuit is prototyped.

Vin = 48V

Vout = 24V

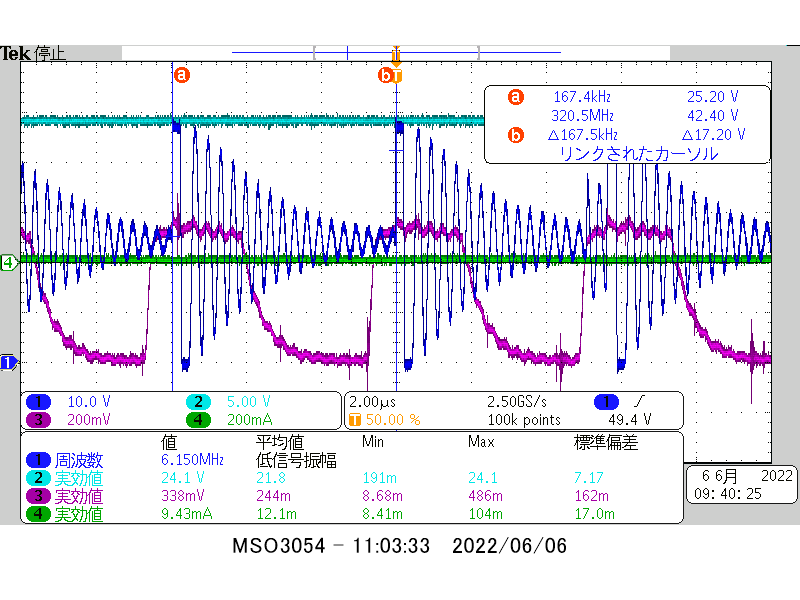

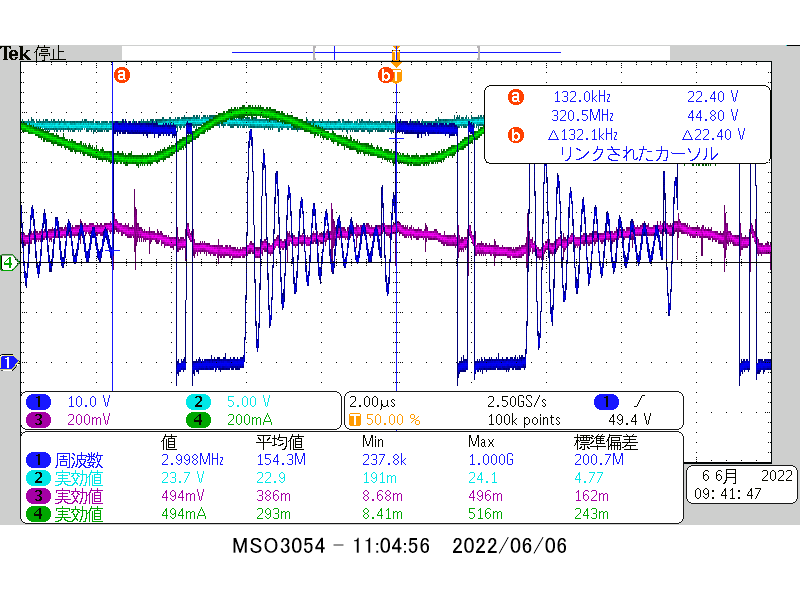

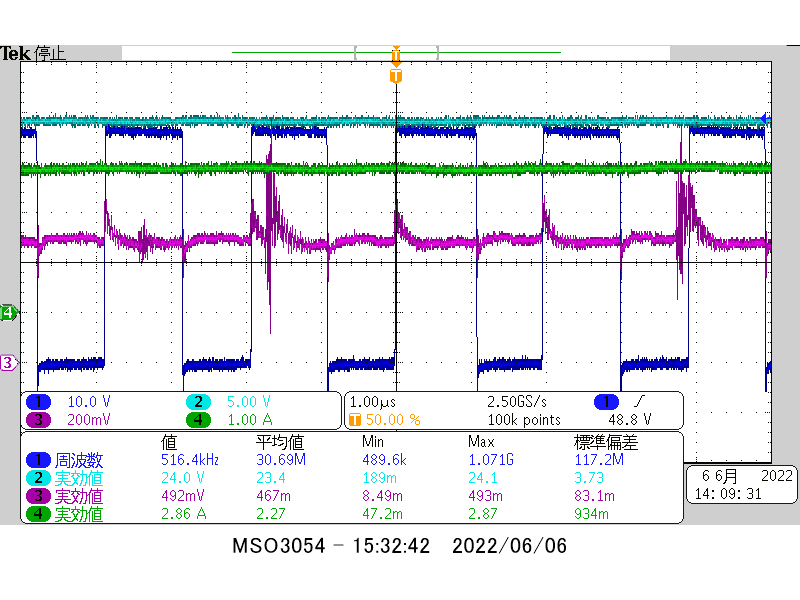

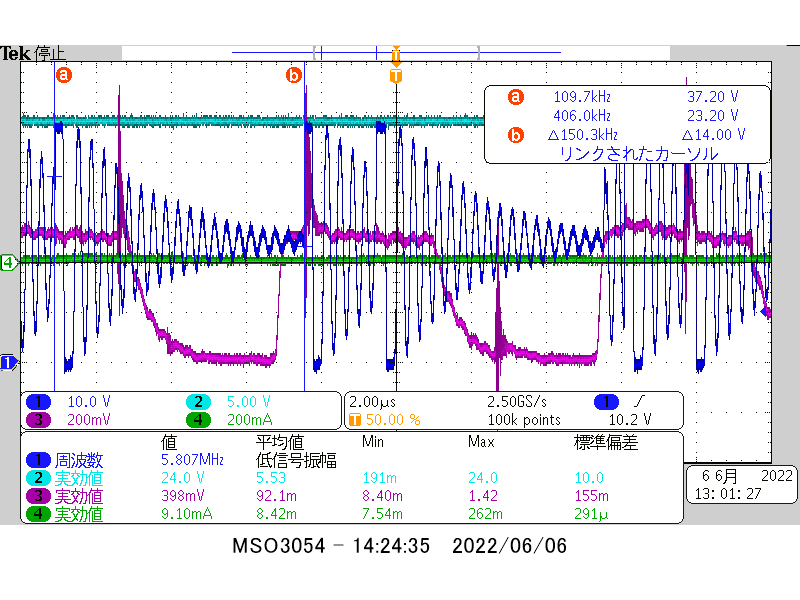

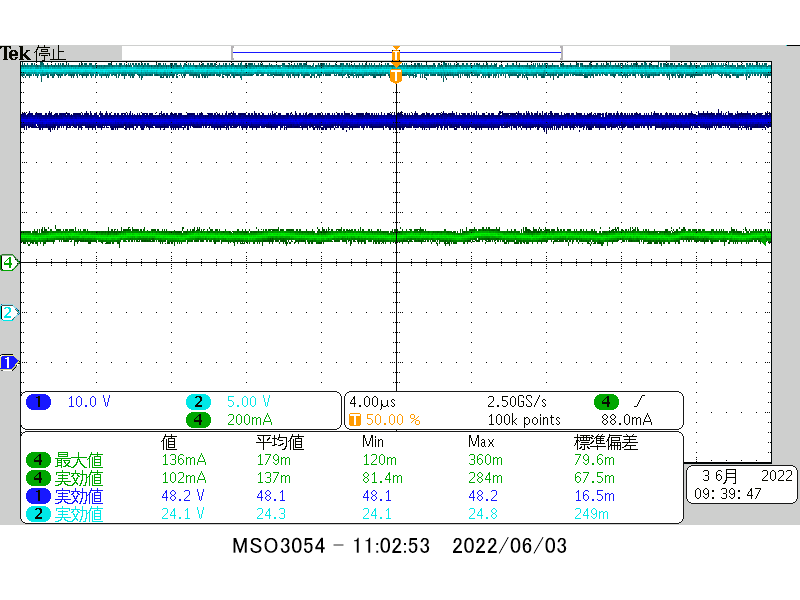

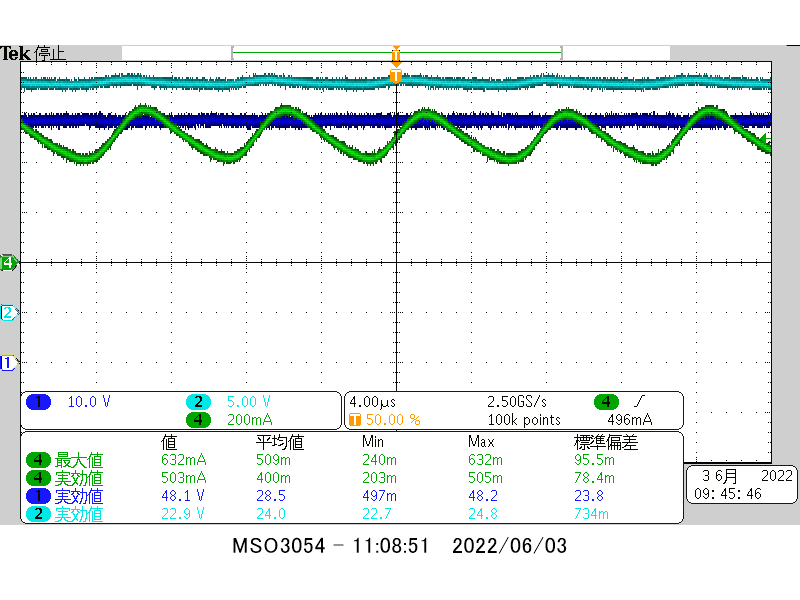

From the measurement results, the output voltage decreased according to the load.

100mA = Vout: 24.1V

500mA = Vout : 22.9V

1ch = Vin

2ch = Vout

3ch = Iout

If Vin=48V, Vout=24V, Iout=3A, and Temp=30°C are set in "WEBENCH", then Cff=560pF, it was better to change to 220pF.

After making this modification, I re-measured, but even under the condition of Iout=1A or so, Vout=22-23V.

Please advise me where I should make the correction.

Best regards .