Other Parts Discussed in Thread: UCC256403, TL431, PFCLLCSREVM034, UCC25630-1EVM-291

Hello,

I’m designing power supply system using UCC256303.

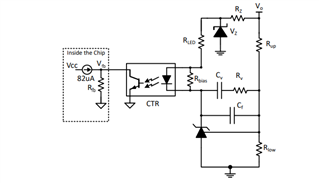

I want to decide the LL/SS-Pin's resistance (RLLupper and RLLlower).

UCC256303's data sheet is written (54page),

"Remove the RLLUpper. In this way, the VLL voltage is at its minimal value 0.7 V, which is determined by the internal circuit design. Then adjust the load current to the desired burst mode threshold load level, and make sure the power stage does not burst in this condition.".

I remove the RLLupper, but I cna not find the RLLlower' value.

How to decide the RLLlower resisrance?

Regards.