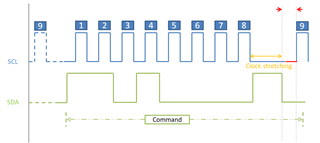

I want to make a time difference between SDA and SCL in ACK stage. What can I do to make SDA pull low early in the I2C clock stretching phase as shown below?

Or SDA pull low longer. What do I do to achieve my goal?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

I want to make a time difference between SDA and SCL in ACK stage. What can I do to make SDA pull low early in the I2C clock stretching phase as shown below?

Or SDA pull low longer. What do I do to achieve my goal?

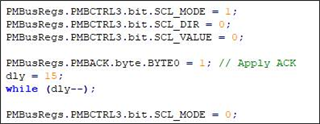

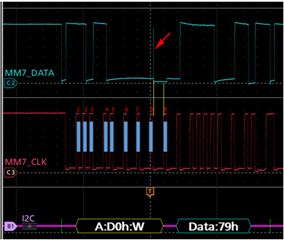

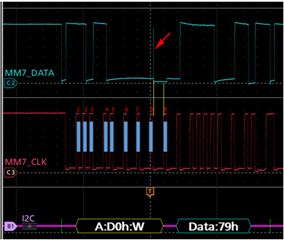

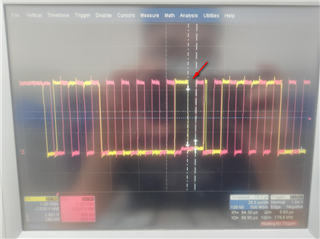

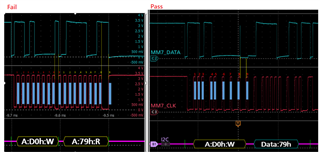

In current design, we use PMBusRegs.PMBACK.byte.BYTE0 to control the ACK. But SDA pulled low is always close to SCL pulled high. As shown below.

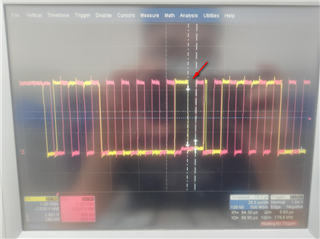

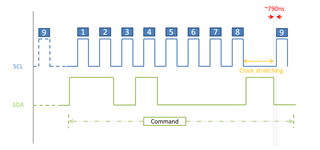

In other chip designs, SDA is pulled low at the end of 8 clocks.

So I want to achieve similar behavior. like this

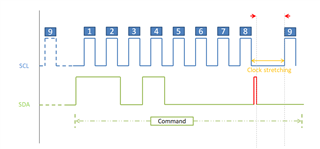

or

Hello,

From PMBus logic point of view, there's no way to control the timing.

One option that may be worth to try is to change the SCL to GPIO mode before ACK so that the SCL is controllable, then switch SCL back to pmbus/i2c mode at a proper time. I'm not sure what would happen, i've never heared about this kind of timing problem. What's the value of pull up resistor you are using? Have you tried to use a smaller resistor, like 1K and 700R?

Best Regards,

Xuemei

The pull-up resistor in the customer system is 1Kohm. Two PSUs from different developers have different results on the same system.

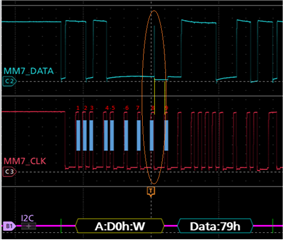

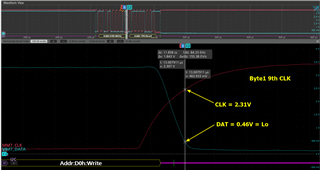

So the customer asked us to solve this problem. The root cause may come from bus delay in system, as shown in the following figure.

So I hope to solve it through firmware. If I change SCL to GPIO mode before ACK as shown below, will I2C module judge abnormal?